The BLAUPUNKT CHASSIS FM100C was an innovative tv set chassis technology.

- First introducing P.I.L. In line CRT TUBE from RCA in 1976.

- Featuring a Switch mode Power supply combined with isolated ground chassis from mains.

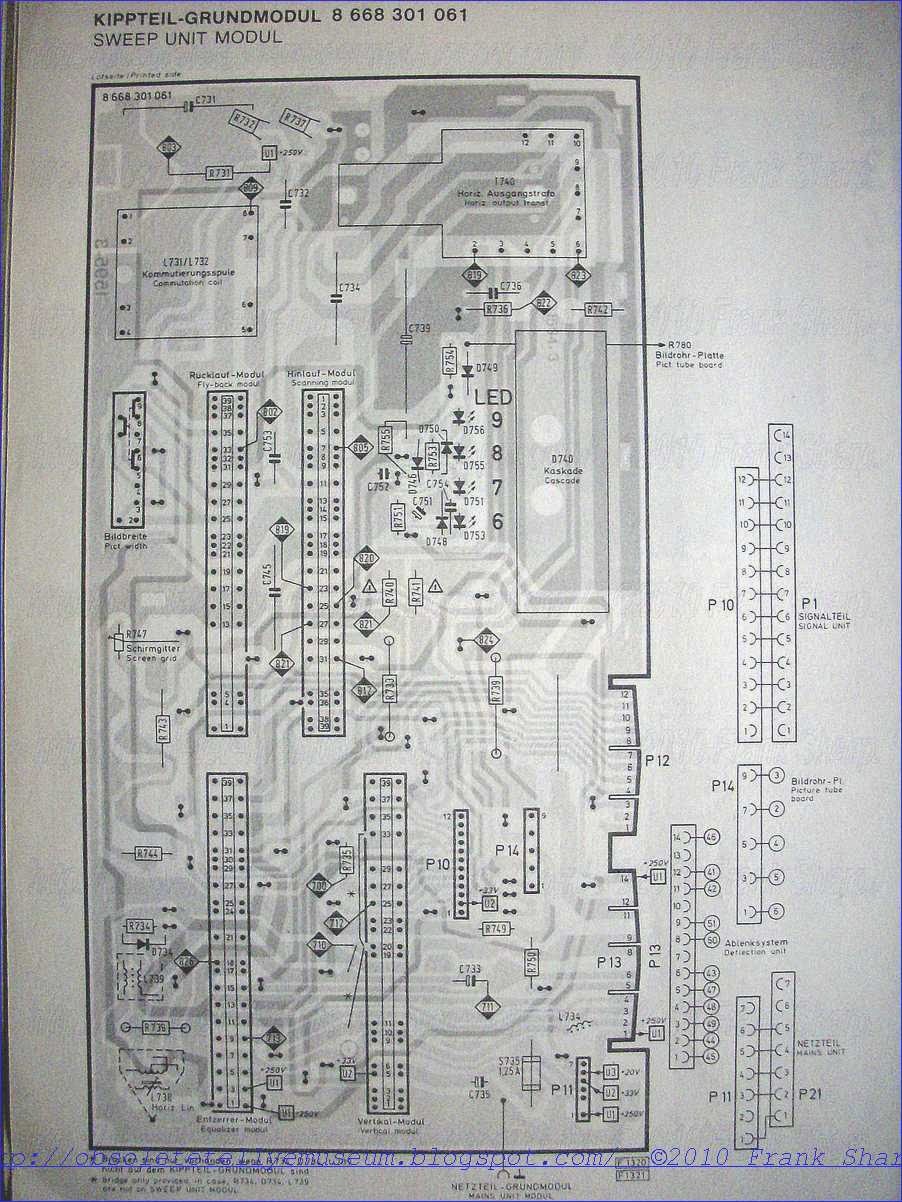

- Led Lamps optical diagnosing system both On Power supply Unit and Deflection Panel Unit see picture above.

- Featuring a OSD Clock Timer and a Channel change program on screen displayed.

- Ultrasonic Remote control.

- Modular concept.

NOTE: The screwdriver is purposely pictured near the power supply Block - Unit to show the

dimensions of it compared to a big size old style screwdriver.

UNITS:

- RGB MODUL 8668 301145

- CHROMA - MODUL 8 668 300 880 MC1327 TBA395 (MOTOROLA)

- LUMINANZ MODUL 8668 300 185 TBA396 (MOTOROLA)

- NF-MODUL 8668300900 TBA120U TBA800

- HOR OSZ.MODUL 8668 300 895 TBA920

- BILD ZF-PLATTE B1591-3 8668 300 860 TDA440

- VERTIKAL MODUL 8668 300941 BD142 TDA1270

- E/W ENTZERR MODUL 8668 300 933

- NETZTEIL 8668 300 953

- STEUER MODUL 8668 300 961

- TUNING DRIVE AND CLOCK FEATURE PCB 8668 811 002

- CLOCK TIMER OSD TV Time / Channel Display Circuits 8668 301 440 AY-5-8320 AY-5-1203A

The line deflection is realized with thyristor tech and the frame deflection is an usual output WITH TDA1270 IC and a complementary output configuration with 2 x BD142

The introduction of l.s.i. MOS integrated circuits has allowed semiconductor manufacturers to include many complex functions on one chip. General Instruments have produced several such chips for the TV industry, amongst the more interesting being the AY-5-8300 8320 series of channel and time display chips. These provide video outputs which superimpose a digital clock or the channel number on the television picture. It's interesting to see how fast semiconductor technology has advanced even in the 70's.

Circuit Description:

The display chip chosen for this post is the AY-5-8320. This provides a four digit clock display with decimal point and a channel number display from 1-16. Both displays appear on a background rectangle for easy viewing. The time and channel displays can be enabled independently. To the display chip we must add a digital clock. This is again an l.s.i. MOS chip, the G.I. AY-5-1203A. Like most digital clocks it uses the 50Hz mains as a clock input, with digital counters to produce the time display output. Pin connections for the two l.s.i. chips, and a typical TV display, are shown on Fig. 1.

The circuit diagram of the digital clock and the character generator is shown on Fig. 2: ICI is the 1203 digital clock chip and IC2 the display chip. The digital clock produces a four -digit output. To transmit this in binary form would require sixteen lines. The clock chip economises on pin connections by sending each digit (four binary bits) in turn. This is called multiplexing. These four binary bits are available at pins 16 to 19 of the 1203. To identify the digits as they are sent, the 1203 provides four multiplex slot signals MX1-4 which appear at pins 3-6. When MX1 is at a

binary 1 the minutes units binary bits are on pins 16 to 19, when MX2 is at a 1 the minutes tens binary bits are present and so on. A strobe output is provided at pin 20. This occurs in the centre of each multiplex slot, and is used by the display chip to gate the data from the clock. The display chip thus obtains and stores all four digits of the time display. The multiplexing frequency is determined by a capacitor (C2) from pin 23 to the positive supply. It is nominally set to 50kHz, although this is not critical. The AY5-8320 display chip IC2 requires (in addition to the time data) line and field sync pulses to position the display, and a 1.1MHz oscillator input. The 1.1MHz oscillator has to be inhibited by the line sync pulse and synchronised on each TV line to prevent ragged edges appearing on the characters. The oscillator consists of the quad CMOS nand IC3, with the frequency of oscillation determined by R3, RV1, C1.

The sync pulses are produced by the sync extraction circuit shown in Fig. 3 (to be described later).

These pulses may be positive -going or negative -going depending on the TV set being used. The circuit requires positive -going line sync pulses at pins 8 and 9 of IC3, and negative -going field sync pulses at pin 7 of IC2. The inverters (IC4 a -d) and the wire links allow the correct polarity signal to be chosen. There is little data available as to what actually goes on inside the 8320 display chip, although it is probably along the lines of the score display article in the September 1975 Practical Wireless . The necessary delays will be generated by digital counters from the 1.1MHz clock. The display chip IC2 produces two outputs, a time output on pin 3 and a background output on pin 2. These are at a binary 1 in the asserted state. These outputs are buffered by IC5 and inverters IC4 e and f to produce the following signals for the video switching: (a) Gate Video. This is at a binary 1 when the normal TV picture is present on its own and at a 0 when the background and time display are added. (b) Gate Time. This is the video output for the time/channel digits and is at a 1 in the asserted state. (c) Background a (IC5 pin 11). This is the background output, inhibited during the time display. It's at a 1 during the background but at a 0 during the time/channel display. (d) Background b (IC4 pin 6). This is a 1 for the entire background and time display. Depending on the colours required for the number and background, the "gate hue" and "gate background" outputs can be taken from background a or b by selecting the corresponding wire links. The time display is produced by taking pin 22 of IC2 to a binary 1. Capacitor C5 keeps the display on for about six seconds after the 1 input is removed. Pin 22 can be triggered by a momentary contact on a push-button or, ultimate luxury, from an ultrasonic remote transmitter.

The time is set by connections A and B. Taking A to a 1 advances the minutes display at two per second; taking B to a 1 similarly advances the hours. The 50Hz clock arrives via C3 and is clipped and buffered by R7, R8, D2, D3. The clock chip IC1 produces at pin 7 a 50kHz burst for 0.5 seconds every second. This is smoothed by R4, D I, C4 and presented to the colon input (pin 20) on the display chip to give a flashing colon display. Some people find flashing colons annoying: if R4, D 1 and C4 are omitted and R6 is inserted the colon becomes steady. The colon output from the clock also drives Tr4 to give a front panel LED display. The colon stops flashing after a power failure, and starts again when either of the set time buttons is pressed. The front panel LED thus indicates that the clock is healthy. The channel data is presented in binary form at terminals W, X, Y, Z, W being the least significant bit. The display is offset by one bit, i.e. 0000 gives 1, 0100 gives 5 and so on. The channel display is enabled by taking terminal V to a binary 1.

Interfacing with the Television Receiver:

Fig. 3 shows the sync extraction circuits and a general purpose video mixing circuit. Before describing these it's probably best to outline the basic requirements of the television interface. The display system needs field and line sync signals from the television receiver. It's highly unlikely that these would be available at the correct levels, and depending on the set and the take off point chosen they can be of either polarity. If oscillograms are shown in the service manual, suitable signals should be easily found - in most if not all television sets. They will probably be found in either the sync separator, the flyback blanking circuits or around the scan output stages. If oscillograms are not available it will be necessary to do a bit of detective work around likely points in the circuit. It's preferable to use scan flyback pulses because of their amplitude and the low source impedance (this avoids loading the sync circuits).

The sync extraction circuits shown in Fig. 3 will accept either positive- or negative -going signals. For negative - going inputs, Trl and Tr2 are forward biased by R14/R18: with positive -going inputs R13/R17 are used instead. The input resistors R12 and R16 form a potential divider with the selected resistor, and the transistors are turned on for positive inputs or off for negative inputs. The wire links shown in Fig. 2 allow the correct polarity signals to be chosen for the display circuit. The values for R12-14 and R16-18 depend on the amplitude of the incoming waveforms. Transistors Tr 1/Tr2 need about 0.1mA base current, so the values will be of the order of 100kS2. This should not load the TV circuit to which it's connected. With some waveforms which are close to or cross OV, capacitors C6 and C7 can be replaced with wire links. If C6 and C7 are used they should be of suitable voltage rating for the circuit to which they are connected. The connection to the video stages presents many options. The majority of colour TV sets today are cathode driven with RGB signals. The description of techniques for interfacing the time display with the set's video circuitry will be mainly directed at cathode drive therefore.

A, typical simple RGB output stage is shown in Fig. 4. The RGB signal from the demodulator i.c. is fed first to a preamplifier or buffer (generally a one transistor stage) then to the high -voltage transistor which drives the appropriate c.r.t. cathode.

A

"brute force and ignorance" method of inserting the time and background

display is to parallel three high - voltage transistors Tr 1 etc. with

the RGB outputs along the lines shown in Fig. 5. The signals driving

these could be

A

"brute force and ignorance" method of inserting the time and background

display is to parallel three high - voltage transistors Tr 1 etc. with

the RGB outputs along the lines shown in Fig. 5. The signals driving

these could bepicked up from the "gate time", "gate background a and b" outputs (Fig. 2). The trimpots RV1 etc. set the current through the output transistors and hence the cathode potentials when the logic signals are at a binary 1. By selection of the right logic signals and suitable settings of the trimpots almost any colour combination for the time and its background could be chosen.

To prevent the display appearing superimposed on the video from unused cathodes, it will again be necessary to resort to brute force. Transistors Tr2 etc. pull down the bases of the buffer preamplifier transistor, turning the television RGB signals off. These transistors are driven from the "background b" signal which is present for the entire display on each line. A more subtle method is to use the 4016 CMOS analogue switch to intercept the video from the demodulator i.c. and substitute in its place the time display. The 4016 i.c. looks like a perfect switch in series with a 300E2 resistor. The switch is controlled by the logic gate input, the switch being closed for a binary 1 and open for a binary 0. The operating time is around 200nS, which is adequate for our application. Cathode drive RGB output stages fall into two categories: direct coupled from the demodulator to. the cathode with clamping earlier in the circuit, or a.c. coupled with clamping at the c.r.t. cathodes. Direct coupled amplifiers are the easiest ones to modify, so these will be dealt with first.

All that's usually required here is to insert the 4016 switch in the base circuit of the output transistor. Fig. 6 shows a suitably modified red drive circuit. Switch SW1 controls the video and SW2 the voltage set by RV1. Switch SW1 is closed by the "gate video" signal from Fig. 2, and SW2 from the selected logic output (gate time, background or hue). The other two amplifiers are dealt with in a similar manner. One small modification is required to the output from the demodulator i.c. This doesn't like having no load, tending to wander off and do its own thing when the video switches are open. To prevent this, a 10k52 resistor should be added from pins 1, 2 and 4 to OV as shown. Next we must deal with a.c. coupled circuits.

A typical example is the tv chassis here described.

The

RGB output circuit (red one) used in this chassis is shown in Fig. 7.

The simplest way to deal with this is to insert the 4016 switch at the

point shown. Because the video is unclamped at this point, the time

display levels will vary according to the picture content. For the best

results it's necessary to clamp the video before substituting the time

display. This is done by the transistor clamp shown in Fig. 7. The video

is a.c. coupled and clamped by Tr 1. The clamp voltage of 4.7V is

chosen to bias the 4016 switches in the centre of their range. The

clamped video is then switched, along with the d.c. levels from the

trimpot RV I, to insert the time display. The modified video is then

a.c. coupled back to 3RV8 on the TV chassis. The 30052 resistance of the

4016 is effectively connected in series with 3RV8 etc. These may

require slight adjustment therefore. Alternatively the dearer 4066 chip

may be used. This is identical to the 4016, but has a resistance of

6052. With the general description over we can turn to the circuit in

Fig. 3. IC6 and IC7 are two quad CMOS switches. IC6 gates the video from

the three demodulator outputs. IC7 gates the levels

on RV2 RV4 to give the three outputs on pins K, L, M. The fourth, Y, is

used in older colour -difference sets and will be described later. The

gating of the levels on RV2 - RV4 is done by the gate logic signals from

Fig. 2. Also shown in F

The

RGB output circuit (red one) used in this chassis is shown in Fig. 7.

The simplest way to deal with this is to insert the 4016 switch at the

point shown. Because the video is unclamped at this point, the time

display levels will vary according to the picture content. For the best

results it's necessary to clamp the video before substituting the time

display. This is done by the transistor clamp shown in Fig. 7. The video

is a.c. coupled and clamped by Tr 1. The clamp voltage of 4.7V is

chosen to bias the 4016 switches in the centre of their range. The

clamped video is then switched, along with the d.c. levels from the

trimpot RV I, to insert the time display. The modified video is then

a.c. coupled back to 3RV8 on the TV chassis. The 30052 resistance of the

4016 is effectively connected in series with 3RV8 etc. These may

require slight adjustment therefore. Alternatively the dearer 4066 chip

may be used. This is identical to the 4016, but has a resistance of

6052. With the general description over we can turn to the circuit in

Fig. 3. IC6 and IC7 are two quad CMOS switches. IC6 gates the video from

the three demodulator outputs. IC7 gates the levels

on RV2 RV4 to give the three outputs on pins K, L, M. The fourth, Y, is

used in older colour -difference sets and will be described later. The

gating of the levels on RV2 - RV4 is done by the gate logic signals from

Fig. 2. Also shown in F ig.

3 is the power supply. This is a fairly conventional i.c. regulator,

made adjustable by the inclusion of Tr3 in the common return line. The

operating voltage range for IC I is 12-18V, for IC2 it's 16-19V, and for

the B picked up from the "gate time", "gate background a and b" outputs

(Fig. 2). The trimpots RV1 etc. set the current through the output

transistors and hence the cathode potentials when the logic signals are

at a binary 1. By selection

of the right logic signals and suitable settings of the trimpots almost

any colour combination for the time series CMOS it's less than 18V. The

supply chosen is 16- 17V therefore. A wire link is included so that the

power supply can be adjusted before it's connected to the rest of the

circuit.

ig.

3 is the power supply. This is a fairly conventional i.c. regulator,

made adjustable by the inclusion of Tr3 in the common return line. The

operating voltage range for IC I is 12-18V, for IC2 it's 16-19V, and for

the B picked up from the "gate time", "gate background a and b" outputs

(Fig. 2). The trimpots RV1 etc. set the current through the output

transistors and hence the cathode potentials when the logic signals are

at a binary 1. By selection

of the right logic signals and suitable settings of the trimpots almost

any colour combination for the time series CMOS it's less than 18V. The

supply chosen is 16- 17V therefore. A wire link is included so that the

power supply can be adjusted before it's connected to the rest of the

circuit.THE TBA800, TBA810 AUDIO integrated circuits:

AUDIO integrated circuits are being increasingly used in television chassis and certainly represent the simplest approach to improving the audio side of a TV set. A number of such i.c.s have appeared during the 70's.

Here describes the use of two fairly recent ones, the SGS-ATES TBA800 and TBA8I0S. Both devices can provide reasonably high outputs into a suitable loudspeaker-the TBA800 will give up to 5W and the TBA810S up to 7W.

The main difference between them being that the TBA800 is a somewhat higher voltage, lower current device. The TBA800 is used in the current Grundig and ASA 110° colour chassis while the Finlux 110' colour chassis uses a TBA810. In each of these chassis the audio i.c. is driven from a TBA120 intercarrier sound i.c. The TBA800 and TBA810S can also be used as the field output stage in 110' monochrome chassis with c.r.t.s of up to l7in. and as the field driver stage in larger screen monochrome sets.

The

TBA800 is designed to provide up to 5W into a 16 Ohm load when operated

from a 24V supply. It is encapsulated in the type cf quad -in -line

case shown in Fig. I: the tabs at the centre are to assist in cooling

the device and must be earthed. The TBA800 can be operated from power

supply voltages up to the absolute maximum permissible value of 30V. It

is best to regard 24V as being the upper limit however in order to

provide an adequate safety margin and prevent possible damage during

voltage surges. The minimum power supply voltage recommended by the

manufacturers is 5V, but the power output is then less than 0-5W. The

quiescent current taken by the TBA800 is typically 9mA from a 24V

supply-no device of this type should draw more than 20mA. When an input

signal is applied the current increases considerably- up to about 1.5A

at full power. Two circuits for use with the TBA800 are shown in Figs. 2

and 3 and give comparable performance. The circuit shown in Fig. 2 is somewhat simpler but that

The

TBA800 is designed to provide up to 5W into a 16 Ohm load when operated

from a 24V supply. It is encapsulated in the type cf quad -in -line

case shown in Fig. I: the tabs at the centre are to assist in cooling

the device and must be earthed. The TBA800 can be operated from power

supply voltages up to the absolute maximum permissible value of 30V. It

is best to regard 24V as being the upper limit however in order to

provide an adequate safety margin and prevent possible damage during

voltage surges. The minimum power supply voltage recommended by the

manufacturers is 5V, but the power output is then less than 0-5W. The

quiescent current taken by the TBA800 is typically 9mA from a 24V

supply-no device of this type should draw more than 20mA. When an input

signal is applied the current increases considerably- up to about 1.5A

at full power. Two circuits for use with the TBA800 are shown in Figs. 2

and 3 and give comparable performance. The circuit shown in Fig. 2 is somewhat simpler but thatshown in Fig. 3 enables one side of the loudspeaker to be connected to chassis. The input resistance of the TBA800 is quite high (typically 5 MOhm) but a resistor must be connected between the input pin 8 and chassis otherwise the out- put stage will not operate with the correct bias. In the circuits shown the volume control VR1 provides this function: the bias current that flows through it is typically 1 microA (maximum 5 microA). The average voltage at the output pin 12 is half the supply potential. The loudspeaker must be capacitively coupled therefore and the low frequency response will be worse as this capacitor is decreased in value. The output coupling capacitor C4 in Fig. 2 also provides the bootstrap connection to pin 4. In Fig. 3 an additional capacitor (C9) is required for this purpose.

In both circuits the value of R1 controls the amount of feedback and thus the gain. The output signal is fed back to pin 6 via an internal 7 kOhm resistor. If R1 is reduced in value the gain will increase but the frequency response will be affected and the distortion will rise. With the component values shown the voltage gain of both circuits is typically 140 (43dB) which is quite adequate for most audio applications. R3 in Fig. 3 is necessary only if the power supply voltage is fairly low (less than about 14V).

C2 smooths the power supply input and C1 is connected between pin 1 and chassis to provide r.f. decoupling and help prevent instability. If mains hum is present on the supply line with the circuit shown in Fig. 3 capacitor C8 should be included between pin 7 and chassis. The circuits shown have a level frequency response (within ±3dB) between about 40Hz and 20kHz. If you wish to reduce the upper 3dB level to about 8kHz C5 can be increased to about 560pF. The total harmonic distortion provided by these circuits remains fairly constant at about 0.5% until the power output reaches 3W: it then rises rapidly with power level as shown in Fig. 4.

The

TBA800 can be operated from a 13V supply to feed up to 2.5W into an 80

load or from a 17V supply to feed the same power into a 160 load without

an additional heatsink. If more output power is required the cooling

tabs must be connected to a heatsink. Two methods of mounting the TBA800

are shown in Figs. 5 and 6. In Fig. 5 the device is inserted into a

circuit board and a heatsink is soldered to the same points as the tabs:

this has the disadvantage that the heatsink extends above the board

though on the other hand the whole board can be used for the

construction of the circuit. In Fig. 6 the tabs are soldered directly to

a suitable area of copper on the board: this method has the

disadvantage that about two square inches of the board are not available

for component mounting. It is generally best to make soldered

connections to the pins of the device since this ensures good heat

dissipation with minimum unwanted feedback. Observe the usual heat

precautions when soldering. The pins can however be carefully bent so

that they will fit into a 16 -pin dual -in -line socket.

The

TBA800 can be operated from a 13V supply to feed up to 2.5W into an 80

load or from a 17V supply to feed the same power into a 160 load without

an additional heatsink. If more output power is required the cooling

tabs must be connected to a heatsink. Two methods of mounting the TBA800

are shown in Figs. 5 and 6. In Fig. 5 the device is inserted into a

circuit board and a heatsink is soldered to the same points as the tabs:

this has the disadvantage that the heatsink extends above the board

though on the other hand the whole board can be used for the

construction of the circuit. In Fig. 6 the tabs are soldered directly to

a suitable area of copper on the board: this method has the

disadvantage that about two square inches of the board are not available

for component mounting. It is generally best to make soldered

connections to the pins of the device since this ensures good heat

dissipation with minimum unwanted feedback. Observe the usual heat

precautions when soldering. The pins can however be carefully bent so

that they will fit into a 16 -pin dual -in -line socket.The TBA810S has the same type of encapsulation as the TBA800 and the connections are also as shown in Fig. 1 except that there is no internal connection to pin 3. An alternative version, the TBA810AS, has two horizontal tabs with a hole in each (see Fig. 7) so that a heatsink can be bolted on. Some readers may find it easier to bolt a heatsink to a TBA810AS than to solder the TBA810S tabs. TBA810 devices can provide 7W of audio power to a 40 loudspeaker when operated from a I6V supply. Fig. 8 shows the change in maximum output power with different supply voltages. As a 4.5W output can be obtained with a 12V supply the TBA810 is much more suitable than the TBA800 for use with battery operated equipment. The TBA810 can provide output currents up to 2.5A.

Two circuits for use with TBA810 devices are shown in Figs. 9 and 10: they are very similar to the circuits shown in Figs. 2 and 3 though some of the capacitor values are larger because of the lower output impedance. The two circuits have comparable performance but that shown in Fig. 10 gives somewhat better results at low supply voltages (down to 4V). In either circuit R2 may be replaced with a 100k0 volume control. The bias current flowing in the pin 8 circuit is typically

0-4 microA and the input resistance 5M 0 (the value of R2 must be much less however to ensure correct bias.

The gain decreases as the value of R1 is increased for the same reason as with the TBA800. The values of R1, C3 and C7 affect the high -frequency response. With the values shown the response is level within ±3dB from about 40Hz to nearly 20kHz. Fig. 11 shows values of C3 plotted against R1 where the frequency is 3dB down at 10kHz and 20kHz and C7 is five times C3. The output distortion with these circuits is about 0.3% for outputs up to 3W rising to about 1% at 4W, 3% at 5W and 9% at 6W with a 14.4V supply voltage. The voltage gain is typically 70 times (37dB). Although this value is half that obtained with the TBA800 the input voltage required to produce a given output power is about the same for both types. This is because a smaller output voltage is required to drive a 40 load at a certain power level than is required to drive a 160 load.

The TBA810S may be mounted in the same way as the TBA800. One way of mounting the TBA810AS is shown in Fig. 12. It is simpler however to bolt flat heatsinks to the tabs.

Devices of this type will be destroyed within a fraction of a second if the power supply is accidentally con- nected with reversed polarity. When experimenting therefore it is wise to include a diode in the positive power supply line to prevent any appreciable reverse current flowing in the event of incorrect power supply connection. The diode can be removed once the circuit has been finalised. The TBA800 is likely to be destroyed if the output is accidentally shorted to chassis. The TBA810S and TBA810AS however are protected from damage in the event of such a short-circuit even if this remains for a long time (but note that the earlier TBA8I0 and TBA810A versions did not contain internal circuitry to provide this protection). The TBA800 is not protected against overheating but the TBA810S and TBA810AS incorporate a thermal shutdown circuit.

For this reason the heat- sinks used with the TBA810S and TBA810AS can have a smaller safety factor than those used with the TBA800. If the silicon chip in a TBA810S or TBA810AS becomes too hot the output power is temporarily reduced by the internal thermal shutdown circuit. As with all high -gain amplifiers great care should be taken to keep the input and output circuits well separated otherwise oscillation could occur. The de- coupling capacitors should be soldered close to the i.c. -especially the 0 1pF decoupling capacitor in the supply line (this should be close to pin I).

Field Output Circuit:

Fig. 13 shows a suggested field output stage for monochrome receivers with 12-17in. 110° c.r.t.s using the TBA81OS. For safe working up to 50°C ambient temperature each tab of the device must be soldered to a square inch of copper on the board. The peak -to - peak scanning current is 1.5A, the power delivered to the scan coils 0.47W, power disspipation in the TBA810S 1 8W, scan signal amplitude 4.1V, flyback amplitude 5V and the maximum peak -to -peak current available in the coils 1.75A

TDA1270 vertical deflection FRAME DEFLECTION INTEGRATED CIRCUITGENERAL DESCRIPTION f The TDA1170 and TDA1270 are monolithic integrated

circuits designed for use in TV vertical deflection systems. They are manufactured using

the Fairchild Planar* process.

Both devices are supplied in the 12-pin plastic power package with the heat sink fins bent

for insertion into the printed circuit board.

The TDA1170 is designed primarily for large and small screen black and white TV

receivers and industrial TV monitors. The TDA1270 is designed primarily for driving

complementary vertical deflection output stages in color TV receivers and industrial

monitors.

APPLICATION INFORMATION (TDA1170)

The vertical oscillator is directly synchronized by the sync pulses (positive or negative); therefore its free

running frequency must be lower than the sync frequency. The use of current feedback causes the yoke

current to be independent of yoke resistance variations due to thermal effects, Therefore no thermistor is

required in series with the yoke. The flyback generator applies a voltage, about twice the supply voltage, to

the yoke. This produces a short flyback time together with a high useful power to dissipated power

MOTOROLA TV ICs DEMODULATION:

........is one operation in a TV receiver that is particularly suited to integration. We saw in other posts the basic differential amplifier circuit-widely used in i.c.s-operating as an f.m. detector in an intercarrier sound i.c.: the circuit functioned as a quadrature detector for the f.m. input signal. The same basic circuit can however be used in other ways to provide demodulation, depending on the inputs applied to it. This post is going to take a look at two Motorola detector i.c.s, the MC1330P which acts as a synchronous detector for the vision and sound signals and the MC1327P which acts as a chroma signal demodulator, RGB matrix and PAL switch. In both these i.c.s differential amplifier circuits are used as double balanced demodulators.

Video Synchronous Demodulator:

The Motorola MC1330P low-level video detector is used in the BLAUPUNKT

COLORADO COLOR 7 665 814 CHASSIS FM100C INTERNAL VIEW. single -standard colour chassis. Fig. 1 shows the i.c. in block diagram form together with the external circuitry as used in the BLAUPUNKT COLORADO COLOR 7 665 814 CHASSIS FM100C INTERNAL VIEW. . The input from the final i.f. stage is fed to an integrated emitter follower at pin 7. This emitter follower provides two drives, one to a limiter amplifier section and the other to the synchronous detector section. As is by now well known a synchronous detector requires two inputs, the signal to be demodulated and a reference signal to provide the switching action. In this case the 39.5MHz i.f. carrier is used as the reference signal. The limiter section removes the modulation and feeds the carrier to the external tuned circuit L108 /C126. The 39.5MHz sinewave is then clipped and applied to the syn- chronous detector section. The detected output is fed to a video preamplifier section which provides across its external load resistors R126 and R232 the 6MHz intercarrier sound feed at pin 5 and the video signal at pin 4. L109 /C129 remove the 6MHz signal from the feed to the luminance and chrominance sections of the receiver.

COLORADO COLOR 7 665 814 CHASSIS FM100C INTERNAL VIEW. single -standard colour chassis. Fig. 1 shows the i.c. in block diagram form together with the external circuitry as used in the BLAUPUNKT COLORADO COLOR 7 665 814 CHASSIS FM100C INTERNAL VIEW. . The input from the final i.f. stage is fed to an integrated emitter follower at pin 7. This emitter follower provides two drives, one to a limiter amplifier section and the other to the synchronous detector section. As is by now well known a synchronous detector requires two inputs, the signal to be demodulated and a reference signal to provide the switching action. In this case the 39.5MHz i.f. carrier is used as the reference signal. The limiter section removes the modulation and feeds the carrier to the external tuned circuit L108 /C126. The 39.5MHz sinewave is then clipped and applied to the syn- chronous detector section. The detected output is fed to a video preamplifier section which provides across its external load resistors R126 and R232 the 6MHz intercarrier sound feed at pin 5 and the video signal at pin 4. L109 /C129 remove the 6MHz signal from the feed to the luminance and chrominance sections of the receiver.The use of this i.c. makes possible a number of basic changes in TV receiver design in the 70's and used about 1982. First, detection is carried out at a much lower level (about 50mV) than is possible using a single diode detector. In addition to providing more linear detection this means that less i.f. gain is required-making up the gain at v.f. is a simple matter. The advantages of this include less need for sound trapping, less critical tuning and more stable i.f. performance.

AFC Output:

The i.c. also provides an output (a 350mV clipped carrier) across the external load resistor R250 to drive an a.f.c. circuit. In the BLAUPUNKT COLORADO COLOR 7 665 814 CHASSIS FM100C INTERNAL VIEW. the a.f.c. circuit consists of a limiter/amplifier stage, discriminator and d.c. amplifier.

Internal Circuit:

The internal circuit of the

MC1330P is shown in Fig. 2. The input emitter -follower is Q4. This drives the differential amplifier pair Q5/Q13 which forms part of the synchronous detector circuit and Q16 which with Q17 forms part of the limiter/amplifier section. The external 39.5MHz tuned circuit is con- nected between the collectors of Q16 and Q17 between which the clipper diodes D1 and D2 are also connected. As a result anti -phase squarewaves appear at the bases of Q8 and Q9 which act as emitter -followers driving Q7 and Q11, and Q10 and Q6, respectively. The double balanced synchronous detector consists of Q6, Q7 and Q5 on one side and Q10, Q11 and Q13 on the other side. The output is developed across the base emitter junction of Q20 which is connected in the collector circuit of Q7 and acts as an emitter -follower to drive the video amplifier section Q23, Q24 and Q25. As we have seen external loads are connected to Q25 at its emitter and collector-providing the main output at pin 4 and an auxiliary output if required at pin 5. The carrier signal for the a.f.c. system is taken from the collector load of Q17 and passed via tabout 20V stabilised is fed in at pin 6 while pin 8

MC1330P is shown in Fig. 2. The input emitter -follower is Q4. This drives the differential amplifier pair Q5/Q13 which forms part of the synchronous detector circuit and Q16 which with Q17 forms part of the limiter/amplifier section. The external 39.5MHz tuned circuit is con- nected between the collectors of Q16 and Q17 between which the clipper diodes D1 and D2 are also connected. As a result anti -phase squarewaves appear at the bases of Q8 and Q9 which act as emitter -followers driving Q7 and Q11, and Q10 and Q6, respectively. The double balanced synchronous detector consists of Q6, Q7 and Q5 on one side and Q10, Q11 and Q13 on the other side. The output is developed across the base emitter junction of Q20 which is connected in the collector circuit of Q7 and acts as an emitter -follower to drive the video amplifier section Q23, Q24 and Q25. As we have seen external loads are connected to Q25 at its emitter and collector-providing the main output at pin 4 and an auxiliary output if required at pin 5. The carrier signal for the a.f.c. system is taken from the collector load of Q17 and passed via tabout 20V stabilised is fed in at pin 6 while pin 8provides the common earthing point.

Chrominance Demodulator:

For chrominance signal demodulation, RGB matrixing and PAL V switching a Motorola type MC1327P i.c. is used in the IRRADIO MOD. 2022/A CORALL 22"

CHASSIS NORDING S4 PAL colour chassis. Fig. 3 shows a block diagram of the i.c. and the surrounding circuitry. The V and U signals, separated in the PAL matrix circuit part of which is shown, are fed in at pins 9 and 8 respectively to separate double balanced chroma synchronous detector circuits which are of the same basic pattern as used in the MC1330P. The U and V reference carriers are fed in at pins 13 and 12 respectively, C178 and R191 giving a 90° shift to the U reference carrier to obtain the correct quadrature conditions. The PAL V switch is built in and is driven by a waveform derived from the ident signal. This is fed in at pin 11. The luminance signal is fed in at pin 3 and line and field blanking pulses at pin 6: blanked RGB outputs are then obtained from emitter followers behind pins 2, 1 and 4 respectively. A 5V peak -to -peak output signal is obtained with an input of 0.3V p -p and the i.c. incorporates a regulated power supply.

CHASSIS NORDING S4 PAL colour chassis. Fig. 3 shows a block diagram of the i.c. and the surrounding circuitry. The V and U signals, separated in the PAL matrix circuit part of which is shown, are fed in at pins 9 and 8 respectively to separate double balanced chroma synchronous detector circuits which are of the same basic pattern as used in the MC1330P. The U and V reference carriers are fed in at pins 13 and 12 respectively, C178 and R191 giving a 90° shift to the U reference carrier to obtain the correct quadrature conditions. The PAL V switch is built in and is driven by a waveform derived from the ident signal. This is fed in at pin 11. The luminance signal is fed in at pin 3 and line and field blanking pulses at pin 6: blanked RGB outputs are then obtained from emitter followers behind pins 2, 1 and 4 respectively. A 5V peak -to -peak output signal is obtained with an input of 0.3V p -p and the i.c. incorporates a regulated power supply.TBA920 line oscillator combination:

DESCRIPTION

DESCRIPTIONThe line oscillator combination TBA920 is a monolithic

integrated circuit intended for the horizontal deflection of the black and white

and colour TV sets

picture tube.

FEATURES:

SYNC-PULSE SEPARATION

OPTIONAL NOISE INVERSION

GENERATION OF A LINE FREQUENCY VOL-

TAGE BY MEANS OF AN OSCILLATOR

PHASE COMPARISON BETWEEN SYNC-

PULSE AND THE OSCILLATOR WAVEFORM

CILLATOR WAVEFORM AND THE MIDDLE OF

THE LINE FLY-BACK PULSE

AUTOMATIC SWITCHING OF THE VARIABLE

TRANSCONDUCTANCE AND THE VARIABLE

TIME C ONSTANT TO ACHIEVE NOISE SUP-

PR ESSION AND, BY SWITCHING OFF, POS-

SIBILITY OF TAPE-VIDEO-REGISTERED RE-

PRODUCTION

SHAPING AND AMPLIFICATION OF THE OS-

CILLATOR WAVEFORM TO OBTAIN PULSES

FOR THE CONTROL OF DRIVING STAGES IN

HORIZONTAL, DEFLECTION CIRCUITS

USING EITHER TRANSISTORS OR THYRISTORS,

BLAUPUNKT COLORADO COLOR 7 665 814 CHASSIS FM100C Controlled power supply for a television receiver equipped with remote control:BLAUPUNKT SWITCH MODE POWER SUPPLY.Blaupunkt-Werke GmbH (Hildesheim, DT)

A single isolation transformer supplies both the remote control receiver and the television receiver. A pulse generator such as a blocking oscillator which energizes the primary winding of the isolation transformer has its pulse width controlled in response to the loading of the circuit of the secondary winding of the isolation transformer, as measured by the voltage across a resistor in the circuit of a primary winding. This measuring resistor is interposed between the emitter of the switching transistor of the blocking oscillator and the receiver chassis. A transistor switching circuit for cutting off the low voltage supply to the scanning circuit oscillators of the television receiver is responsive to the output of the remote control receiver, to a signal from an operating control of the television receiver, and to an indication of overcurrent in the picture tube, independently.

1. A power supply circuit for a television receiver equipped for remote control comprising, in combination:

an on-off switch for connecting and disconnecting the television receiver and its power supply circuit respectively to and from the electricity supply mains;

pulse generating means arranged for energization through said on-off switch;

an isolation transformer having its primary winding supplied with the output of said pulse generating means;

a power conversion circuit connected to the secondary winding of said isolation transformer for energization thereby, for supplying an operating voltage for the scanning circuits of the television receiver and for supplying a plurality of other voltages to said receiver, at least one of which other voltages is also supplied to said scanning circuits;

a remote control signal receiver for remote control of said television receiver and controlled switching means responsive to said remote control receiver for switching said television receiver between a stand-by condition and an operating condition, both said remote control receiver and said controlled switching means being connected to a secondary winding of said isolation transformer for energization thereby, said controlled switching means having a switching path for connecting and disconnecting said scanning circuits of said television receiver respectively to and from a source of said operating voltage in said power conversion circuit and

means for reducing energy transfer through said pulse generating means to said isolation transformer when said television receiver is in the stand-by condition.

2. A power supply circuit as defined in claim 1, in which said pulse generating means includes rectifying means energized through said on-off switch for supplying direct current for energization of said pulse generating means. 3. A power supply circuit as defined in claim 2, in which said energy transfer reducing means includes means for varying the width (duration) of pulses generated by said pulse generating means in response to the extent of loading of the secondary circuit of said isolating transformer as measured in the primary circuit of said transformer. 4. A power supply circuit as defined in claim 2, in which said pulse generating means includes a blocking oscillator and said energy transfer reducing means includes means for reducing the width (duration) of the pulses generated by said blocking oscillator. 5. A power supply circuit as defined in claim 4, in which said blocking oscillator includes a switching transistor (5) and a load measuring resistor (7) interposed in a connection between the emitter of said switching transistor and the receiver chassis, and in which said pulse width reducing means is responsive to the voltage drop across said load measuring resistor. 6. A power supply circuit as defined in claim 5, in which said pulse width reducing means includes a controllable resistance (10) in the circuit of said blocking oscillator controlled in response to the voltage drop across said load measuring resistor. 7. A power supply circuit as defined in claim 1, in which said operating voltage connected and disconnected to said scanning circuits by said controlled switching means is the low voltage supply voltage (U 3') of the line scan and picture scan oscillators of the television receiver and in which said controlled switching means is controlled so as to switch off said low voltage supply voltage to put the television receiver in the stand-by condition. 8. A power supply circuit as defined in claim 7, in which said controlled switching means includes a first switching transistor (15) at the collector of which there is applied a direct current supply voltage (U 3) energized through said isolating transformer and a second switching transistor (24) for controllably short-circuiting the base bias of said first switching transistor, whereby a stabilized low voltage (U 3') exists at the emitter of said first switching transistor (15) when a positive signal is supplied from an operating control of the television receiver or from said remote control receiver to the base of said second switching transistor (24). 9. A power supply circuit as defined in claim 7, in which said controlled switching means is responsive independently to an overcurrent condition in the picture tube for switching off said low voltage supply voltage (U 3') in response to said overcurrent condition.

In recent times television receivers have frequently been provided with ultrasonic remote control devices for the purpose of offering easier control. As more and more television receivers are utilized in combination with additional equipment, it becomes increasingly necessary to connect the receivers only indirectly to the electric power mains (house wiring). In a known advantageous solution of this problem, a power supply unit includes an isolating transformer which is wired up with a blocking oscillator in the primary circuit. The blocking oscillator is supplied with a d-c voltage which is obtained by rectification of the supply voltage. Compared to the isolating transformers which are directly mains-operated, these so-called switch-mode power supply units have the advantage that they can be made in considerably smaller size, as they are operated at a significantly higher frequency, and the further advantage that they require less expensive means for rectification.

It is necessary to supply television receivers equipped with ultrasonic remote control with the possibility for a stand-by operation in which only the ultransonic receiver is supplied with power and, in some cases, also the heating current for the picture tube. Usually a separate power supply unit is provided for the ultrasonic receiver and the heating of the picture tube, a unit that includes an isolating transformer of its own, the primary winding of which is directly mains-fed. Upon transition from normal operation to stand-by operation, the power supply unit of the blocking osciallator is switched off, so that the television receiver receives only the relatively small quantity of energy required for the ultrasonic receiver and, in some cases, also for the heating of the picture tube.

Because of the required second isolating transformer, this known circuit has the disadvantages that it requires both greater space and greater expenditure.

It is the object of the present invention to develop a simplified power supply unit which does not have the above-mentioned disadvantages.

SUMMARY OF THE INVENTION

Briefly, the television receiver and the ultrasonic receiver are connected to the same isolating transformer; means for the switching from normal operation to stand-by operation and vice versa are placed in the secondary circuit of the isolating transformer, and means are arranged in the primary circuits of the isolating transformer for reducing the amount of energy made available for stand-by operation purposes.

The main advantages of the present invention are that no separate isolating transformer is required for supplying the current during the stand-by operation, and that, during the stand-by operation, it is nevertheless only the power required for this operation which is consumed.

An advantageous embodiment of the present invention obtains reduction of the energy quantum transmitted through the power supply during stand-by by reduction of the pulse width of the pulses generated by the blocking oscillator.

Another advantageous embodiment of the present invention utilizes measurement in the primary circuit of the isolating transformer of variation in load occurring in the secondary circuit as a control variable for determining the pulse width.

A further advantageous embodiment of the present invention obtains the control variable for the pulse width across a measuring resistor interposed in the connection of the emitter of the switching transistor of the blocking oscillator to the chassis.

Still another advantageous embodiment of the present invention provides that the voltage drop across the measuring resistor controls a controllable resistor.

The advantageous embodiments described above offer highly simple and advantageous possibilities for measuring the variation in load upon switching between normal and stand-by operation, as well as for the consequent control of the energy transmitted via the isolating transformer.

The possibility of a simple and inexpensive switching between normal and stand-by operation is achieved by effecting the switching between normal and stand-by operation by means of switching on or switching off, respectively, the low voltage supply of the line scan oscillator, and, especially, by a first switching transistor which short-circuits the base bias of a second switching transistor at the collector of which a direct current supply voltage is present and at the emitter of which a stabilized low voltage exists, when a positive signal is supplied from the operating control of the television receiver or from the remote control receiver to the base of the first switching transistor.

The circuit arrangements just mentioned offer the advantage that they may simultaneously be utilized as a protective circuit. This is achieved by a switching-off device for the low voltage which can also be triggered at any time by a signal built up by overcurrent in the picture tube.

BRIEF DESCRIPTION OF THE DRAWINGS

The invention is further described by way of illustrative example by reference to the annexed drawings in which:

FIG. 1 is a circuit diagram, partly in block form, of an embodiment of the invention;

FIG. 2 is a circuit diagram of one form of means for interrupting the power to the picture circuits in the stand-by condition in connection with the circuit of FIG. 1, and

FIG. 3 is a circuit diagram of one way of controlling the pulse width of the blocking oscillator 4 in response to the switching circuit 8 in the circuit of FIG. 1.

DESCRIPTION OF THE PREFERRED EMBODIMENT

An on-off power switch 2 of the television receiver is connected to the supply terminals 1, providing a primary operating control for the receiver. Consquently, the supply voltage is also present at the output of the operating control 2 when the television receiver is turned on thereby, and arrives at a rectifying stage 3 comprising means for rectifying and smoothing the supply current as well as for suppressing interference. A d-c voltage, feeding a blocking oscillator stage 4, is present at the output of the recifying stage 3. The main part of the blocking oscillator 4, symbolically represented in FIG. 1 by a fragmentary circuit diagram, is a switching transistor 5, in the load circuit of which the primary winding of an isolating tranformer 6 is placed. A measuring resistor 7 is connected between the emitter of the switching transistor 5 and the chassis, across which measuring resistor a voltage is taken and applied to a load-dependent control circuit 8. The voltage taken at the measuring resistor 7 is fed via a resistor 9 to the base of a transistor 10 which serves as a controllable load for the blocking oscillator 4. A resistor 11 and a capacitor 12, each of which is connected to chassis with its other terminal, are also connected to the base of the transistor 10. The emitter of transistor 10 is connected to chassis, while the collector of the transistor 10 is connected back to the blocking oscillator stage 4.

An on-off power switch 2 of the television receiver is connected to the supply terminals 1, providing a primary operating control for the receiver. Consquently, the supply voltage is also present at the output of the operating control 2 when the television receiver is turned on thereby, and arrives at a rectifying stage 3 comprising means for rectifying and smoothing the supply current as well as for suppressing interference. A d-c voltage, feeding a blocking oscillator stage 4, is present at the output of the recifying stage 3. The main part of the blocking oscillator 4, symbolically represented in FIG. 1 by a fragmentary circuit diagram, is a switching transistor 5, in the load circuit of which the primary winding of an isolating tranformer 6 is placed. A measuring resistor 7 is connected between the emitter of the switching transistor 5 and the chassis, across which measuring resistor a voltage is taken and applied to a load-dependent control circuit 8. The voltage taken at the measuring resistor 7 is fed via a resistor 9 to the base of a transistor 10 which serves as a controllable load for the blocking oscillator 4. A resistor 11 and a capacitor 12, each of which is connected to chassis with its other terminal, are also connected to the base of the transistor 10. The emitter of transistor 10 is connected to chassis, while the collector of the transistor 10 is connected back to the blocking oscillator stage 4. In the secondary circuit of the isolating transformer 6, a d-c voltage supply stage or power conversion circuit 13 is placed, substantially consisting of a rectifying circuit 14, which, in the example shown, is provided with six outputs at which the voltages U 1 to U 5 can be taken off with respect to the sixth output connected to the chassis. At the terminal U 3, there is, in addition, a branch feeding both the collector-to-emitter path of the transistor 15 and also, through a resistor 16, the collector-to-emitter path of the transistor 15a. The emitter of the transistor 15a is directly connected to the base of transistor 15. The emitter of the transistor 15 is connected to chassis via a series connection of a resistor 17, a potentiometer 18, and a further resistor 19. The tap of the potentiometer 18 is connected to the base of a further transistor 20. The transistor 20 is connected to chassis by means of its emitter via a Zener diode 21, the collector of the transistor 20 controlling the base of the transistor 15a. The emitter of the transistor 20 is connected to the emitter of the transistor 15 via a resistor 22. A terminal for tapping off the voltage U 3' is connected to the emitter of the transistor 15.

The base of the transistor 15a is connected to a switching stage 23 responsive to a remote control ultrasonic receiver by a conductor leading to the collector of a switching transistor 24 which is connected to chassis via its emitter. The base of the switching transistor 24 is connected to an input terminal 28 leading into the television receiver via two resistors 25, 26 and a capacitor 27 connected in series, that input terminal 28 passing on switching signals from the receiver to the switching transistor 24, as will be explained in more detail below.

The cathode of a diode 29, which is connected to chassis via its anode, is connected to the junction point of the resistor 26 and the capacitor 27. The junction point of the two resistors 25, 26 is connected to chassis via a capacitor 30. The base of the switching transistor 24 is connected to chassis via a resistor 31. Furthermore, that base electrode is also connected to a terminal 32 to which an electrical switching signal is applied which is either built up in response to an ultrasonic signal received by the remote control receiver 32' or is supplied from an operating control of the television receiver. At the terminal 32, the switching transistor 24 receives the signal containing the information whether the television receiver is to work in the normal operating condition, i.e. to receive and process the sound and video signals, or in the stand-by condition in which it is substantially only the ultrasonic receiver that is supplied with current.

When a positive signal arrives at the base of the switching transistor 24, the latter becomes conductive, and causes chassis potential to be present at the base of transistor 15a. The transistor 15 is thereby blocked, and there is no longer any voltage at the terminal U 3'. Since the voltage U 3' serves as an operating voltage for the line and picture scan oscillator, the deflecting stages of the receiver cannot work and no high voltage and other related supply voltages are generated at the line circuit transformer. In consequence, by means illustrated diagrammatically in

FIG. 2, the electric circuits connected to the terminals U 1 to U 3 are interrupted. The voltages U 4 and U 5 serve for supplying the ultrasonic receiver, i.e. they are required for the stand-by operation.

FIG. 2, the electric circuits connected to the terminals U 1 to U 3 are interrupted. The voltages U 4 and U 5 serve for supplying the ultrasonic receiver, i.e. they are required for the stand-by operation. In case no counteracting means should be provided for, the variation in load would cause a voltage rise in the secondary circuit of the isolating transformer 6, which effect is, of course, not desired. Therefore, a measuring resistor is connected in the primary circuit in the emitter line of the switching transistor 5 of the blocking oscillator 6, the variation in load in the secondary circuit appearing at the measuring resistor 7 as a current variation. The current change thus produced, causes a variation in the base bias of the transistor 10, the capacitor 12 having an integrating effect to avoid undesired effects due to interference pulses and abrupt load fluctuations.

The change of the working point of the transistor 10 causes a change in the pulse width in the blocking oscillator stage 4, as more fully shown in FIG. 3, so that the energy quantum transmitted via the isolating transformer 6 is such that the required voltages are present in the secondary circuit. It should also be mentioned that the load-dependent switch 8 and the circuit of FIG. 3 are represented only by way of illustration and that many circuit arrangements may be devised by straight-forward application of known principles for controlling the pulse width.

The circuit connected between the terminal 28 and the base of the switching transistor 24 serves as a part of a protective circuit for the picture tube. Any overcurrent is measured at the low-end resistor 31 of the high-voltage cascade in conventional techinque. The voltage thus produced is fed to the base of the switching transistor 24, and causes the television receiver to be switched over to stand-by operation, so that no damage can be done to the picture tube. Thus, the device performing the switching between normal operation and stand-by operation is advantageously and simultaneously utilized as a protective circuit. The circuit 23, as shown, provides for stabilizing the potential at the base of transistor 24 and for integrating such possibly occurring overload peaks as are not intended to triggering the protective circuit.

Using the circuit diagram according to FIG. 3 it is possible in a simple manner to control the pulse width of the blocking oscillator 4 in response to the switching circuit 8.

According to the circuit diagram of FIG. 2 the terminal U1 is connected to a line scan oscillator circuit 40, the terminal U2 to a picture scan oscillator circuit 41 and the terminal U3 to a circuit 42 for a sound output stage. The circuits 40, 41, 42 get their operating voltage from the terminal U3'. If the operating voltage U3' is zero, the circuits 40, 41, 42 are interrupted. In this case the voltages at the terminals U1, U2, U3 remain.

The described circuit of this invention for controlling the voltage in the secondary circuit of the isolating transformer 6 offers the advantage that it is exclusively arranged in the primary circuit, and, therefore, permits an uncomplicated design which is easy to realize. To control the pulse width by measuring the load fluctuations at the low-end resistor of the switching transistor 5, represents a very useful means for control since, thereby the transmitted energy can effectively and easily be controlled.

The blocking oscillator stage 4 shown in detail in FIG. 3 incorporates an externally triggered blocking oscillator arranged to be triggered through an oscillator operating preferably at the line scanning frequency, which is to say its wave form is not particularly critical and it should be provided with means to keep it in step with the line scanning frequency, as is known to be desirable. The transistors 51 and 52 of the triggered output stage of the blocking oscillator circuit could be regarded as constituting a differential amplifier the inputs of which are defined by the base connections of the respective transistors 51 and 52. The input voltage applied to the base connection of transistor 52 is the Zener voltage of the Zener diode 53, thus a constant reference voltage. The operating voltage for the transistors 51 and 52 and for the Zener diode 53 is obtained from the supply voltage UB, which is to say from the rectifier 3. The diode 67 protects the transistor 52, for example at the time of the apparatus being switched on, against damage from an excessively high emitter-base blocking voltage. The capacitor 65 prevents undesired oscillation of the circuit of transistors 51 and 52, which could give rise to undesired disturbances.

At the base of the transistor 51, there is present as input voltage for the circuit a composite voltage that is the sum of three voltages. These are, first, the line scan frequency trigger voltage coupled through the capacitor 63; second, a bias voltage dependent upon the loading of the blocking oscillator stage resulting from the load on the secondary of the transformer 6, but detected by the voltage across the resistor 7 and actually controlled by the load-sensitive control circuit 8, and, third, a regulating voltage applied at the terminal 71 of the resistor 70, which regulating voltage is proportional to the voltage of the secondary winding of the transformer 6 and can accordingly be provided by one or another of the output circuits of the rectifier 14 of FIG. 1 or by a separate winding of the transformer 6 and a separate rectifier element connected in circuit therewith. This regulating voltage and the control voltage provided by the control circuit 8 are applied to the resistor 61 which completes the circuit for both of these bias voltages and their combined effect constitutes the bias voltage for the transistor 51 which determines its working point.

The circuit of the transistors 51 and 52 operates as an overdriven differential amplifier. When the trigger voltage exceeds the threshold determined by the base voltage of the transistor 51, the circuit produces an approximately rectangular output voltage pulse of constant amplitude. Since the trigger voltage is recurrent, the result is a periodic succession of rectangular output voltage pulses, but the duration or pulse width of these pulses depends upon the loading and the output voltage of the stage. The output voltage of the circuit constituted by the transistors 51 and 52 comes from the emitter connection of the transistor 52 and is furnished to the switching transistor 5, preferably through a driver stage 54, such as a transformer or another transistor stage for better matching of the circuit impedances. Of course, the collector circuit of the transistor 5 includes the primary winding of the transformer 6 of FIG. 1.

The described power supply unit thus represents a well functioning component subject to but a small number of potential sources of error, due to the simple design, and permits considerable reduction of costs in comparison with circuits and equipment heretofore known.

BLAUPUNKT COLORADO COLOR 7 665 814 CHASSIS FM100C INTEGRAL THYRISTOR-RECTIFIER DEVICE: AEG TD3F 700 R34A semiconductor switching device comprising a silicon controlled rectifier (SCR) and a diode rectifier integrally connected in parallel with the SCR in a single semiconductor body. The device is of the NPNP or PNPN type, having gate, cathode, and anode electrodes. A portion of each intermediate N and P region makes ohmic contact to the respective anode or cathode electrode of the SCR. In addition, each intermediate region includes a highly conductive edge portion. These portions are spaced from the adjacent external regions by relatively low conductive portions, and limit the conduction of the diode rectifier to the periphery of the device. A profile of gold recombination centers further electrically isolates the central SCR portion from the peripheral diode portion.

That class of thyristors known as controlled rectifiers are semiconductor switches having four semiconducting regions of alternate conductivity and which employ anode, cathode, and gate electrodes. These devices are usually fabricated from silicon. In its normal state, the silicon controlled rectifier (SCR) is non-conductive until an appropriate voltage or current pulse is applied to the gate electrode, at which point current flows from the anode to the cathode and delivers power to a load circuit. If the SCR is reverse biased, it is non-conductive, and cannot be turned on by a gating signal. Once conduction starts, the gate loses control and current flows from the anode to the cathode until it drops below a certain value (called the holding current), at which point the SCR turns off and the gate electrode regains control. The SCR is thus a solid state device capable of performing the circuit function of a thyratron tube in many electronic applications. In some of these applications, such as in automobile ignition systems and horizontal deflection circuits in television receivers, it is necessary to connect a separate rectifier diode in parallel with the SCR. See, for example, W. Dietz, U. S. Pat. Nos. 3,452,244 and 3,449,623. In these applications, the anode of the rectifier diode is connected to the cathode of the SCR, and the cathode of the rectifier is connected to the SCR anode. Thus, the rectifier diode will be forward biased and current will flow through it when the SCR is reverse biased; i.e., when the SCR cathode is positive with respect to its anode. For reasons of economy and ease of handling, it would be preferable if the circuit function of the SCR and the associated diode rectifier could be combined in a single device, so that instead of requiring two devices and five electrical connections, one device and three electrical connections are all that would be necessary. In fact, because of the semiconductor profile employed, many SCR's of the shorted emitter variety inherently function as a diode rectifier when reverse biased. However, the diode rectifier function of such devices is not isolated from the controlled rectifier portion, thus preventing a rapid transition from one function to the other. Therefore, it would be desirable to physically and electrically isolate the diode rectifier portion from that portion of the device which functions as an SCR.

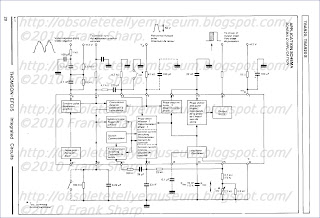

BLAUPUNKT COLORADO COLOR 7 665 814 CHASSIS FM100C LINE / HORIZONTAL DEFLECTION WITH THYRISTOR SWITCH TECHNOLOGY OVERVIEW.

Horizontal deflection circuit

(Thyristor Horizontalsteuerung)

Description:

1. A horizontal deflection circuit for generating the deflection current in the deflection coil of a television picture tube wher

ein a first switch controls the horizontal sweep, and wherein a second switch in a so-called commutation circuit with a commutating inductor and a commutating capacitor opens the first switch and, in addition, controls the energy transfer from a dc voltage source to an input inductor, characterized in that the input inductor (Le) and the commutating inductor (Lk) are combined in a unit designed as a transformer (U) which is proportioned so that the open-circuit inductance of the transformer is essentially equal to the value of the input inductor (Le), while the short-circuit inductance of the transformer (U) is essentially equal to the value of the commutating inductor (Lk), and that the second switch (S2) is connected in series with the dc voltage source (UB) and a first winding (U1) of the transformer (U). 2. A horizontal deflection circuit according to claim 1, characterized in that the transformer (U) operates as an isolation transformer between the supply (UB) and the subcircuits connected to a second winding. 3. A horizontal deflection circuit according to claim 1, characterized in that the second switch (S2) is connected between ground and that terminal of the first winding (U1) of the transformer (U) not connected to the supply potential (+UB). 4. A horizontal deflection circuit according to claim 1, characterized in that a capacitor (CE) is connected across the series combination of the first winding (U1) of the transformer and the second switch (S2). 5. A horizontal deflection circuit according to claim 1, characterized in that the second winding (U2) of the transformer (U) is connected in series with a first switch (S1), the commutating capacitor (Ck), and a third, bipolar switch (S3) controllable as a function of the value of a controlled variable developed in the deflection circuit. 6. A horizontal deflection circuit according to claim 5, characterized in that the third switch (S3) is connected between ground and the second winding (U2) of the transformer. 7. A horizontal deflection circuit according to claim 2, characterized in that the isolation transformer carries a third winding via which power is supplied to the audio output stage of the television set. 8. A horizontal deflection circuit according to claims 2, characterized in that the voltage serving to control the first switch (S1) is derived from a third winding of the transformer.

The present invention relates to a horizontal deflection circuit for generating the deflection current in the deflection coil of a television picture tube wherein a first switch controls the horizontal sweep, and wherein a second switch in a so-called commutation circuit with a commutating inductor and a commutating capacitor opens the first switch and, in addition, controls the energy transfer from a dc voltage source to an input inductor.

German Aus

The first controlled switch also forms part of a second branch circuit where it is connected in series with a second current source and a reactance capable of oscillating. When the first switch is closed, the reactance, consisting essentially of a coil and a capacitor, receives energy from the second current source during a fixed time interval. This energy which is taken from the second current source corresponds to the circuit losses caused during the previous deflection cycle.

As can be seen, such a circuit needs two different, separate inductive elements, it being known that inductive elements are expensive to manufacture and always have a certain volume determined by the electrical properties required.

The object of the invention is to reduce the amount of inductive elements required.

The invention is characterized in that the input inductor and the commutating inductor are combined in a unit designed as a transformer which is proportioned so that the open-circuit inductance of the transformer is essentially equal to the value of the input inductor, while the short-circuit inductance of the transformer is essentially equal to the value of the commutating inductor, and that the second switch is connected in series with the dc voltage source and a first winding of the transformer.

This solution has an added advantage in that, in mass production, both the open-circuit and the short-circuit inductance are reproducible with reliability.

According to another feature of the invention, the electrical isolation between the windings of the transformer is such that the transformer operates as an isolation transformer between the supply and the subcircuits connected to a second winding or to additional windings of the transformer. In this manner, the transformer additionally provides reliable mains isolation.

According to a further feature of the invention, the second switch is connected between ground and that terminal of the first winding of the transformer not connected to the supply potential. This simplifies the control of the switch.

According to a further feature of the invention, to regulate the energy supply, the second winding of the transf

ormer is connected in series with the first switch, the commutating capacitor, and a third, bipolar switch controllable as a function of the value of a controlled variable developed in the deflection circuit.

The advantage gained by this measure lies in the fact that the control takes place on the side separated from the mains, so no separate isolation device is required for the gating of the third switch. Further details and advantages will be apparent from the following description of the accompanying drawings and from the claims. In the drawings,

FIG. 1 is a basic circuit diagram of the arrangement disclosed in German Auslegeschrift (DT-AS) No. 1,537,308;

FIG. 2 shows a first embodiment of the horizontal deflection circuit according to the invention, and

FIG. 3 shows a development of the horizontal deflection circuit according to the invention.

FIG. 1 shows the essential circuit elements of the horizontal deflection circuit known from the German Auslegeschrift (DT-AS) No. 1,537,308 referred to by way of introduction.

Connected in series with a dc voltage source UB is an input inductor Le and a bipolar, controlled switch S2. In the following, this switch will be referred to as the "second switch"; it is usually called the "commutating switch" to indicate its function.

In known circuits, the second switch S2 consists of a controlled rectifier and a diode connected in inverse parallel.

The second switch S

2 also forms part of a second circuit which contains, in addition, a commutating inductor Lk, a commutating capacitor Ck, and a first switch S1. The first switch S1, controlling the horizontal sweep, is constructed in the same manner as the above-described second switch S2, consisting of a controlled rectifier and a diode in inverse parallel. Connected in parallel with this first switch is a deflection-coil arrangement AS with a capacitor CA as well as a high voltage generating arrangement (not shown). In FIGS. 1, 2, and 3, this arrangement is only indicated by an arrow and by the reference characters Hsp. The operation of this known horizontal deflection circuit need not be explained here in detail since it is described not only in the German Auslegeschrift referred to by way of introduction, but also in many other publications.

FIGS. 2 and 3 show the horizontal deflection circuit modified in accordance with the present invention. Like circuit elements are designated by the same reference characters as in FIG. 1.

FIG. 2 shows the basic principle of the invention. The two inductors Le and Lk of FIG. 1 have been replaced by a transformer U. To be able to serve as a substitute for the two inductors Le and Lk, the transformer must be proportioned in a special manner. Regardless of the turns ratio, the open-circuit inductance of the transformer is chosen to be essentially equal to the value of the input inductor Le, and the short-circuit inductance of the transformer is essentially equal to the value of the commutating inductor Lk.

To permit the second switch S2 to be utilized for the connection of the dc voltage source UB, it is included in the circuit of that winding U1 of the transformer connected to the dc voltage UB.

In principle, it is of no consequence for the operation of the switch S2 whether it is inserted on that side of the winding U1 connected to the positive operating potential +UB or on the side connected to ground. In practice, however, the solution shown in FIGS. 2 and 3 will be chosen since the gating of the controlled rectifier is less problematic in this case.

In compliance with pertinent safety regulations, the transformer U may be designed as an isolation transformer and can thus provide mains separation, which is necessary for various reasons. It is known from German Offenlegungschrift (DT-OS) No. 2,233,249 to provide dc isolation by designing the commutating inductor as a transformer, but this measure is not suited to attaining the object of the present invention.

If the energy to be taken from the dc voltage source is to be controlled as a function of the energy needed in the horizontal deflection circuit and in following subcircuits, the embodiment of the horizontal deflection circuit of FIG. 3 may be used.

The circuit including the winding U2 of the transformer U contains a third controlled switch S3, which, too, is inserted on the grounded side of the winding U2 for the reasons mentioned above. This third switch S3, just as the second switch S2, is operated at the frequency of a horizontal oscillator HO, but a control circuit RS whose input l is fed with a controlled variable is inserted between the oscillator and the switch S3. Depending on this controlled variable, the controlled rectifier of the third switch S3 can be caused to turn on earlier. A suitable controlled variable containing information on the energy consumption is, for example, the flyback pulse capable of being taken from the high voltage generating circuit (not shown). Details of the operation of this kind of energy control are described in applicant's German Offenlegungsschrift (DT-OS) No. b 2,253,386 and do not form part of the present invention.

With mains isolation, the additional, third switch S3 shown here has the advantage of being on the side isolated from the mains and eliminates the need for an isolation device in the control lead of the controlled rectifier.

As an isolation transformer, the transformer U may also carry additional windings U3 and U4 if power is to be supplied to the audio output stage, for example; in addition, the first switch S1 may be gated via such an additional winding.

The points marked at the windings U1 and U2 indicate the phase relationship between the respective voltages. Connected in parallel with the winding U1 and the second switch S2 is a capacitor CE which completes the circuit for the horizontal-frequency alternating current; this serves in particular to bypass the dc voltage source or the electrolytic capacitors contained therein.

If required, a well-known tuning coil may be inserted, e.g. in series with the second winding U2, without changing the basic operation of the horizontal deflection circuit according to the invention.