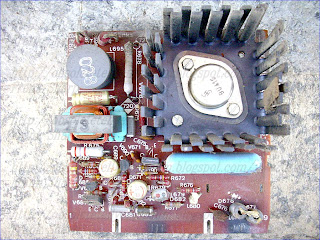

This is the first version of the FM100 MODULAR CHASSIS FROM SIEMENS BLAUPUNKT.

This here was using the Memotronic Tuning system based on Motorola tuning memory.

The CHASSIS FM100 is a modular chassis and introduces severals improvements compared to earlyer types:

The CHASSIS FM100 is a modular chassis and introduces severals improvements compared to earlyer types:SSVD TECH AND

more integration in video stages and if stages.

Phasing out the Thyristor technology for line stages.

The CHASSIS FM100 delivers a totally uncommon Frame deflection system,

Plus the E/W Correection circuit uses the same Technology.

It's a system called S.S.V.D. which stays for Synchronized Switched Vertical Deflection.

The system is highly reliable and does dissipate energy like linear amplifier types like A class or AB class Types and should

not be confused with D Class amplifier.

not be confused with D Class amplifier.Abstract:

a horizontal deflection circuit including first means for generating horizontal rate energy signals;

a vertical deflection winding;

energy storage capacitance means coupled to said vertical deflection winding;

first and second switching means coupled to said first means and said energy storage capacitance means; and

second means coupled to said first and second switching means for switching conductive states of both of said switching means for coupling successively smaller portions of said horizontal rate energy signals to said energy storage capacitancemeans during a first part of a vertical trace interval and successively larger portions of said horizontal rate energy signals during a second part of said vertical trace interval for developing a vertical deflection current in said vertical deflectionwinding during said vertical trace interval,

said second means causing said first switching means to conduct during a vertical retrace interval for coupling substantial portions of said horizontal rate energy signals to said energy storage capacitance means during said vertical retraceinterval for preventing undesired oscillations within said horizontal deflection circuit.

2. A system according to claim 1 wherein said first and second switching means comprise controlled semiconductors, said second means coupling first and second signals to said first and second switching means for switching conductive states ofboth of said controlled semiconductors.

3. A system according to claim 2 wherein said second means includes transformer means for coupling said first signals to said first switching means.

4. A system according to claim 3 wherein said first switching means comprises a silicon controlled rectifier, a secondary winding of said transformer means coupled between the gate and cathode electrodes of said silicon controlled rectifier.

5. A system according to claim 2 including vertical signal means coupled to said second means for generating a vertical rate signal for modulating said first and second signals at a vertical rate.

6. A system according to claim 5 wherein said vertical signal means includes first circuitry for generating a component of said vertical rate signal that inhibits conduction of said second switching means during said vertical retrace interval.

7. A system according to claim 6 wherein said first circuitry comprises an RC differentiating circuit.

8. A system according to claim 7 wherein the time constant of said differentiating circuit is selected to provide a duration for said component of said vertical rate signal substantially equal to said vertical retrace interval.

8. A system according to claim 7 wherein the time constant of said differentiating circuit is selected to provide a duration for said component of said vertical rate signal substantially equal to said vertical retrace interval.9. In a television receiver including a horizontal deflection circuit comprising a horizontal deflection generator and a horizontal output transformer, a switched vertical deflection circuit comprising:

a vertical deflection winding;

energy storage capacitance means coupled to said vertical deflection winding;

first and second controllable switches coupled to said capacitance means and to respective secondary windings of said horizontal output transformer for coupling horizontal retrace signals to said capacitance means; and

a modulator coupled to said first and second controllable switches and responsive to a source of vertical rate signals for providing to said controllable switches during said vertical trace interval horizontal rate signals modulated at a verticalrate for varying the amount of each horizontal retrace signal coupled to said capacitance means for generating a vertical deflection current in said vertical deflection winding during said vertical trace interval, said switched vertical deflectioncircuit substantially loading said horizontal deflection circuit at the beginning and end of said vertical trace interval,

said modulator providing signals to said first controllable switch during said vertical retrace interval for coupling said horizontal retrace signals to said capacitance means during said vertical retrace interval for substantially loading saidhorizontal deflection circuit during said retrace interval for preventing undesired oscillations within said horizontal deflection circuit.

10. A circuit according to claim 9 wherein said vertical rate signals cause said modulator to provide for conduction of said first controllable switch during said vertical retrace interval and for inhibiting conduction of said second controllable swith during said vertical retrace interval.

A switched vertical deflection circuit comprises a horizontal deflection circuit including apparatus for generating horizontal rate energy signals, a vertical deflection winding, an energy storage capacitance, first and second switches and aswitching circuit coupled to the switches. The switching circuit switches the conductive states of the switches for coupling successively smaller portions of the horizontal rate energy signals to the energy storage capacitance during a first part of thevertical trace interval and successively larger portions during a second part for developing a vertical deflection current in the vertical deflection winding during the vertical trace interval. The switching circuit causes the first switch to conductduring the vertical retrace interval for coupling substantial portions of the horizontal rate energy signals to the energy storage capacitance during the vertical retrace interval for preventing undesired oscillations within the horizontal deflection circuit.

A switched vertical deflection circuit comprises a horizontal deflection circuit including apparatus for generating horizontal rate energy signals, a vertical deflection winding, an energy storage capacitance, first and second switches and aswitching circuit coupled to the switches. The switching circuit switches the conductive states of the switches for coupling successively smaller portions of the horizontal rate energy signals to the energy storage capacitance during a first part of thevertical trace interval and successively larger portions during a second part for developing a vertical deflection current in the vertical deflection winding during the vertical trace interval. The switching circuit causes the first switch to conductduring the vertical retrace interval for coupling substantial portions of the horizontal rate energy signals to the energy storage capacitance during the vertical retrace interval for preventing undesired oscillations within the horizontal deflection circuit.1. In a television receiver,

having means (1, 2) coupling out a portion of the energy delivered by the horizontal deflection circuit during line flyback or retrace;

a vertical deflection output stage (V) including deflection means (LV1, LV2) and a charge capacitor element (C);

and a sawtooth wave generator (S), which controls application of the coupled-out energy derived from the horizontal deflection circuit to the vertical deflection means (LV1, LV2), a method to control vertical deflection

comprising, in accordance with the invention, the step of

additionally controlling application of the energy to the vertical deflection means by the sawtooth wave generator during the vertical flyback or retrace interval by reversely re-charging said capacitor element during said interval.

2. Method according to claim 1, wherein the re-charging step is carried out continuously.

3. Method according to claim 1, wherein the re-charging step is carried out linearly.

4. Method accordi

ng to claim 1, wherein the vertical deflection output stage includes, vertical deflection coil elements (LV1, LV2) and forming with said charge capacitor element (C) said deflection means, a feedback resistor element (R) and a vertical correction circuit element (4), said charge capacitor element and said other elements being connected to form a parallel oscillatory circuit;

ng to claim 1, wherein the vertical deflection output stage includes, vertical deflection coil elements (LV1, LV2) and forming with said charge capacitor element (C) said deflection means, a feedback resistor element (R) and a vertical correction circuit element (4), said charge capacitor element and said other elements being connected to form a parallel oscillatory circuit; said method including the step of controlling the damping of the parallel oscillatory circuit by controlling the relative parameters of said elements.

5. In a television receiver, a vertical deflection system including means (1, 2) coupling out a portion of the energy delivered by the horizontal deflection circuit during line flyback or retrace;

a vertical deflection output stage (V) including vertical deflection means (LV1, LV2);

and a sawtooth wave generator (S) controlling application of the coupled-out energy to the vertical deflection means during the flyback interval

and wherein, in accordance with the invention,

the time constant (τS) of the sawtooth wave generator (S) is longer than the time constant (τV) of the vertical deflection output stage (V).

6. Vertical deflection system according to claim 5, wherein the time constant of the vertical deflection output stage is about twice as long as that of the sawtooth wave generator (S).

7. Vertical deflection system according to claim 5, wherein the ratio of time constants (τS /τV) is between about 1.5 to 2.5.

8. Vertical deflection system according to claim 5, wherein the vertical deflection output stage (V) includes a charge capacitor element (C), vertical deflection coil elements (LV1, LV2) forming said vertical deflection means, a feedback resistor element (R) and a vertical correction circuit element (4), said elements being connected to form a parallel oscillatory circuit;

and wherein said oscillatory circuit is a damped oscillatory circuit.

9. Vertical deflection system according to claim 8, wherein the elements of said oscillatory circuit are dimensioned to provide a time constant which is about half of the time constant of the sawtooth wave generator (S) and is in the order of about 0.5 ms.

Video scanning in television receivers is effected, as well known, by a vertical deflection circuit. A pulse generator is synchronized by pulses included in the video signal. The pulses are then applied over a pulse generator, a driver and an output stage to deflection systems, usually deflection coils.

Various types of solid-state circuits have been proposed; for example, U.S. Pat. No. 4,048,544 describes a transistorized vertical deflection circuit with additional circuitry to stabilize the pulses. The time constant of the pulse generator and of the driver stage of such circuits is less than

the time constant of the output or final power stage of the vertical deflection circuit. Such vertical deflection circuits have some disadvantages, particularly in that the transistors are operated at high voltages which may result in flash-over and thus damage or destruction of the transistor. The power required to control the final output transistors is already substantial and thus the overall operating efficiency of such a vertical deflection circuit is low.

the time constant of the output or final power stage of the vertical deflection circuit. Such vertical deflection circuits have some disadvantages, particularly in that the transistors are operated at high voltages which may result in flash-over and thus damage or destruction of the transistor. The power required to control the final output transistors is already substantial and thus the overall operating efficiency of such a vertical deflection circuit is low. In earlier developments, a vertical deflection circuitry was proposed which avoids some of the disadvantages of this transistorized circuit; in this earlier circuit, a portion of the energy contained in the horizontal flyback is coupled out and is directly utilized in order to supply current for the vertical deflection coils. To control application of current, a controlled sawtooth wave generator is connected to the final output stage of the vertical deflection circuit, the sawtooth wave generator having a short retrace or flyback time. These vertical deflection circuits also have some disadvantages. The energy derived for vertical deflection is obtained from the horizontal flyback; thus, changes in loading in the vertical deflection circuitry affect the horizontal output stage. The vertical deflection circuit is subject to substantial changes in loading during the vertical flyback or retrace since, in accordance with the previously known circuit, the vertical deflection circuit is not controlled during the vertical flyback or retrace. The lack of control of the vertical deflection circuit causes abrupt changes in loading which result in undesired spurious oscillations in the vertical output stage. These oscillations can so feed back or react on the horizontal output stage that the horizontal flyback pulses are overloaded, the vertical stage starts to oscillate, and high voltages may occur therein during the vertical flyback. This, necessarily, degrades the image quality of the reproduced video picture. High-voltage flash-over may occur and electronic components, particularly solid-state semiconductor elements can be destroyed thereby.

It is an object of the present invention to provide a vertical deflection circuit for television receivers, which has the advantages of utilizing a portion of the energy contained in the horizontal deflection circuit during horizontal flyback without causing abrupt changes in loading on the horizontal output stage and preventing undesired spurious and uncontrolled oscillation of the vertical output stage.

SUBJECT MATTER OF THE PRESENT INVENTION

Briefly, the sawtooth wave generator which controls charging of a charge capacitor of the vertical output stage is controlled to in turn control the charge on the capacitor also during vertical retrace; in accordance with a feature of the invention, this control is obtained by so arranging and relatively matching the time constants of the sawtooth wave generator and of the parallel oscillatory circuit formed by the vertical deflection coils of the T.V. receiver and the charge capacitor that the time constant of the vertical deflection output stage is less, preferably about half that of the time constant of the sawtooth wave generator. This matching can be obtained by so selecting the values of the components of the vertical deflection output stage that the resulting oscillatory circuit formed by the capacitor, resistance elements in the circuit, and the vertical deflection output stage form a damped oscillatory circuit.

The invention will be described by way of example with reference to the accompanying drawings, wherein the single FIGURE is a schematic diagram of a vertical deflection output stage in which the method of the present inv

ention is carried out, and utilizing the system thereof.

ention is carried out, and utilizing the system thereof. A horizontal deflection output stage 1 is connected to a horizontal output transformer 2 which has coupling windings W 1 and W 2 to derive a portion of the energy contained in the line retrace. This energy is stored in the inductances L 1 and L 2 and then applied through thyristors Th 1 and Th 2 to a charge capacitor C. A control circuit 3 is provided triggering the thyristors Th 1 and Th 2 in such a manner that the charge capacitor C is positively charged during the first half of the video scan and negatively during the second half of the video scan. The charge capacitor C is discharged through the vertical deflection coils L V1 and L V2 , a vertical correction circuit 4 for vertical correction and a feedback resistor R. The voltage drop across feedback resistor R is fed back to the control circuit 3 in order to ensure exact triggering of the thyristors Th 1 and Th 2 and to control the desired deflection current.

Positive deflection current is obtained during the first half of the video scan by the triggered thyristor Th 1 ; negative deflection current is derived during the second half of the video scan by the triggered thyristor Th 2 . The thyristors Th 1 and Th 2 can be triggered during a portion of the video scan simultaneously to result in a linear deflection and provide overlapping, opposite deflection currents.

The control circuit 3, together with the thyristors Th 1 and Th 2 , and the inductances L 1 and L 2 , forms a sawtooth wave generator S. The vertical deflection output stage V is formed of the vertical deflection

coils L V1 , L V2 , the vertical correction circuit 4, the charge capacitor C and the feedback resistor R. As can be seen from the FIGURE, the capacitor C on the one hand, and the deflection coils, the correction circuit 4 and the resistor R on the other hand form a parallel oscillatory circuit.

coils L V1 , L V2 , the vertical correction circuit 4, the charge capacitor C and the feedback resistor R. As can be seen from the FIGURE, the capacitor C on the one hand, and the deflection coils, the correction circuit 4 and the resistor R on the other hand form a parallel oscillatory circuit. The circuit, as far as the diagram is concerned, is known. Uncontrolled, undesired and spurious oscillations in the horizontal output stage can be avoided, in accordance with the invention, by reverse re-charging the capacitor C also during the vertical retrace interval. This re-charging of the capacitor C preferably is carried out continuously and desirably linearly. The controlled re-charging of the capacitor C can be readily obtained by arranging the relative values of the components in the sawtooth wave generator S and in the vertical output stage V such that the time constant τ S of the sawtooth wave generator is longer than the time constant τ V of the vertical deflection output stage. Mathematically: τ S >τ V (1)

preferably, the quotient of the time constants should be between 1.5 and 2.5, most desirably about 2, mathematically: 1.5>τ S /τ V <2.5 (2)

if the time constants of the respective circuits are properly arranged, the thyristors Th 1 and Th 2 can be precisely triggered also during the short time interval of the vertical flyback or retrace. Due to the short time constant, the vertical deflection circuit can then follow the control from the control circuit 3 exactly; the voltage dropped across the feedback resistor R will permit precise triggering, with respect to time, of the thyristors Th 1 and Th 2 also during the vertical flyback. In the first half of the video scan, the thyristor Th 2 is triggered; in the second half, thyristor Th 1 is triggered. This ensures linear flyback.

The time constant τ V is essentially determined by the vertical deflection coils L V1 , L V2 , the correction circuit 4, and the feedback resistor R which, together with the capacitor C, form a parallel oscillatory circuit. A short time constant corresponds to high damping of this parallel oscillatory circuit. Thus, in accordance with a feature of the present invention, by suitably arranging the ratio of the time constants, the parallel oscillatory circuit will not start undesired uncontrolled oscillations which could interfere with image reproduction quality, or proper operation of the components of the T.V. receiver. The ratio of the time constants can be selected by suitable adjustment of t

he damping of the oscillatory circuit.

he damping of the oscillatory circuit. The vertical deflection circuit has an essentially continuous, uniform and even power requirement. This avoids abrupt changes in loading during the vertical retrace. Excessive over-compensation of horizontal flyback pulses, and resulting high voltages which may lead to undesired distortion of the reproduced image and possibly to damage or destruction of components of the video system are avoided. The vertical deflection circuitry, as described, can be readily manufactured and has high operating reliability. The efficiency is high and the power requirement is low.

Various changes and modifications may be made within the scope of the inventive concept.

In a typical T.V. receiver using vertical deflection coils of 20 millihenry inductance, a suitable time constant τ V is 0.5 ms. In such a circuit, the resistor R can have a value 1 Ω capacitor C a value of 1.5 μF. and the reflected impedance of correction circuit 4 a value of 1 Ω.

The sawtooth wave generator has a time constant of 1 ms, providing for a slow rise time for 20 milliseconds. The circuit 3 is well known and described in U.S. Pat. No. 4,048,544.

SIEMENS BILDMEISTER FC524 (7 667 279) CHASSIS FM100 Switched vertical deflection system SSVD CIRCUIT THEORY EXPLANATION :

CHASSIS FM100

First and second controllable switching stages are respectively coupled between a source of horizontal retrace pulses and a capacitor connected across a vertical deflection winding. A modulator is coupled to the switching stages for controlling the timing of conduction thereof relative to the timing of the horizontal retrace pulses. One switching stage charges the capacitor in one polarity with pulses of current of gradually decreasing amplitude and duration during a first portion of the vertical trace interval and the other switching stage charges the capacitor in the opposite polarity with pulses of current of gradually increasing amplitude and duration during a second portion of the vertical trace interval. The capacitor supplies scanning current of first and second polarities to the vertical deflection winding during respective first and second portions of each vertical trace interval.

1. In a deflection system for cathode ray tubes, said deflection system of the type including a horizontal deflection circuit for deflecting an electron beam of said cathode ray tube in a horizontal direction in response to a horizontal deflection wave, a vertical deflection circuit comprising:

a vertical deflection winding responsive to a sawtooth current therethrough for deflecting said electron beam of said cathode ray tube in a vertical direction; and

means for applying successively smaller portions of the energy of said horizontal deflection wave during one interval of said vertical deflection and successively greater portions of said energy of said horizontal deflection wave during a second interval of said vertical deflection to said vertical deflection circuit for producing all of said sawtooth current in said vertical deflection winding, said first and second intervals occurring during the trace portion of each vertical deflection interval.

2. A vertical deflection circuit according to claim 1 wherein said means include controllable switches coupled to said horizontal deflection circuit and to said vertical deflection circuit for providing a current path for said horizontal retrace pulses therebetween. 3. A vertical deflection circuit according to claim 2 wherein a capacitor is coupled in parallel with said vertical deflection winding and to said controllable switches for being charged by said horizontal retrace pulses through said controllable switches and for supplying said sawtooth current in said vertical deflection winding. 4. A vertical deflection circuit according to claim 3 wherein first and second inductances are respectively coupled to first and second of said controllable switches and to said capacitor to form first and second series resonant circuits for charging said capacitor with said horizontal retrace pulse energy. 5. A vertical deflection circuit according to claim 4 wherein said resonant frequency of said first and second series resonant circuits is less than said horizontal rate frequency. 6. A vertical deflection circuit according to claim 5 wherein the resonant frequency of said capacitor in parallel with said vertical deflection winding has a period substantially equal to twice the vertical deflection circuit retrace interval. 7. A vertical deflection circuit according to claim 6 wherein said horizontal deflection retrace pulses are obtained from transformer windings in said horizontal deflection circuit coupled to said first and second controllable switching means. 8. A vertical deflection circuit according to claim 7 wherein modulator means responsive to vertical and horizontal deflection rate signals produce first and second trains of horizontal rate pulses the leading edges of which are successively and respectively delayed from and advanced toward the leading edge of said horizontal deflection retrace pulses and coupled to said first and second controllable switches for respectively controlling the conduction thereof. 9. A vertical deflection circuit according to claim 8 wherein said modulator

means produces said first and second trains of horizontal rate pulses which overlap during said vertical deflection interval. 10. A switched vertical deflection system comprising:

means produces said first and second trains of horizontal rate pulses which overlap during said vertical deflection interval. 10. A switched vertical deflection system comprising: a first series circuit including first and second switches, first and second sources of horizontal deflection rate voltage and first and second inductors;

a capacitor;

a second series circuit including said first switch, said first source of horizontal rate voltage, said first inductor and said capacitor;

a third series circuit including said second switch, and second source of horizontal rate voltage, said second inductor and said capacitor;

modulator means responsive to horizontal and vertical deflection rate signals for producing overlapping series of respective increasing and decreasing width horizontal rate pulses during each vertical deflection cycle respectively coupled to said first and second switches for controlling the conduction thereof for charging said capacitor to a first polarity through said second series circuit and to a second polarity through said third series circuit, said first series circuit conducting current of first and second polarities from said second and third series circuits such that only the amplitude difference between said first and second currents charges said capacitor when said pulses overlap; and

a vertical deflection winding coupled to said capacitor for providing a discharge path therefor for producing a substantially linear sawtooth alternating current in said deflection winding during each vertical deflection cycle.

11. A switched vertical deflection system for producing a sawtooth current in a vertical deflection winding, comprising:

a first series circuit including a first switch, a first source of horizontal retrace pulses, a first inductor and capacitor, said first source of horizontal retrace pulses being poled to cause current to flow in a direction to charge said capacitor in a first polarity direction, said first inductor and said capacitor being tuned to a frequency lower than the frequency of said horizontal retrace pulses;

a second series circuit including a second switch, a second source of horizontal retrace pulses, a second inductor and said capacitor, said second source of horizontal retrace pulses being poled to cause current to flow in a direction to charge said capacitor in a second polarity direction, said second inductor and said capacitor being tuned to a frequency lower than the frequency of said horizontal retrace pulses;

a vertical deflection winding coupled in parallel with said capacitor to form a parallel resonant circuit having a period substantially equal to twice the desired vertical retrace interval;

a source of signals having a frequency equal to the desired vertical deflection rate;

a modulator coupled to receive said horizontal retrace pulses and to said source of signals having a frequency equal to said desired vertical deflection rate for producing first and second sets of timing pulses, said first set of timing pulses occurring during the first half of said sawtooth current interval and having leading edges which occur increasingly later than the leading edges of said retrace pulses, said second set of timing pulses occurring during the second half of said sawtooth current interval and having leading edges which occur increasingly closer to the leading edges of said retrace pulses; and

means coupling said first and second sets of timing pulses to said first and second switches, respectively, for initiating conduction of current through said switches at the time of said leading edges of said timing pulses during said sawtooth current interval.

This invention relates to vertical deflection circuits and more particularly to switched mode vertical deflection circuits.

Most vertical deflection systems for television receiver use include linear amplifiers for amplifying a sawtooth voltage wave. The output stages in such systems may use single-ended or push-pull circuit configurations for driving a sawtooth of current through the vertical deflection winding. Measurements have shown that the vertical deflection output stage dissipates power in amounts which in some cases may be up to twice or more of the power consumed by the deflection winding.

More efficient vertical deflection circuits have been proposed utilizing class-D operated amplifier output circuits. In a class-D amplifier the output transistors are operated as switches, and since the transistors usually are either nonconducting or saturated when so operated, the power dissipation in the transistors is reduced. To achieve the required vertical rate scanning current waveform, it is common to pulse-width modulate a higher frequency signal, such as the horizontal rate signal or a multiple thereof, at the vertical deflection rate and use these pulse-width modulated signals to drive the class-D output stages. To remove the horizontal rate component from the vertical scanning current sometimes it is necessary to utilize filter networks which consume a relatively large amount of power, thereby offsetting the advantages of a class-D amplifier to some extent.

Another serious consideration in the use of class-D amplifiers is the minimizing of crossover distortion. Crossover distortion occurs when the scanning current sawtooth waveform is not linear when it passes through zero and reverses polarity at the middle of the vertical trace interval. Such distortion resulting from the nonlinear current manifests itself as an increased intensity horizontal bar across the center of the viewing screen. In other situations in which the class-D circuits produce a horizontal rate triangular current component on the vertical scanning current a diagonal line may appear on the viewing screen.

SUMMARY OF THE INVENTION

A vertical deflection circuit includes switches which are controlled for applying successively smaller portions of the horizontal retrace pulse energy during one portion of the vertical deflection cycle and successively greater portions of the horizontal retrace pulse energy during another portion of the vertical deflection cycle to the vertical deflection winding for developing a sawtooth current therein.

A more complete description of the invention together with a description of additional advantages thereof is given in the following description in conjunction with the accompanying drawing of which:

FIG. 1 is a schematic and block circuit diagram of a switched vertical deflection system embodying the invention;

FIGS. 2a-2h illustrate waveforms obtained at various points in the system of FIG. 1;

FIG. 3 is a more detailed schematic and block circuit diagram of a switched vertical deflection system embodying the invention;

FIGS. 4a-4c illustrate waveforms obtained at various points in the circuit of FIG. 3;

FIG. 5 is a detailed block and schematic circuit diagram of another switched vertical deflection system embodying the invention; and

FIGS. 6a-6f illustrate waveforms obtained at various points in the circuit of FIG. 5.

DESCRIPTION OF THE INVENTION

FI

G. 1 shows a switched mode vertical deflection circuit which, for example, may be incorporated in a television receiver. Horizontal sync pulses 5 from a sync separator, not shown, are coupled to an input terminal 6 of a horizontal deflection generator 7. Horizontal deflection generator 7 may be any suitable type for supplying horizontal deflection current to a horizontal deflection winding 11 mounted adjacent to a cathode ray tube 10 as well as supplying horizontal rate pulses for various functions within a television receiver. A primary winding 8a of a horizontal output and high voltage transformer 8 receives energy from generator 7. A tertiary winding 8d of transformer 8 supplies retrace pulses to a high voltage multiplier and rectifier assembly 9 which provides a high DC voltage to the ultor terminal of cathode ray tube 10.

G. 1 shows a switched mode vertical deflection circuit which, for example, may be incorporated in a television receiver. Horizontal sync pulses 5 from a sync separator, not shown, are coupled to an input terminal 6 of a horizontal deflection generator 7. Horizontal deflection generator 7 may be any suitable type for supplying horizontal deflection current to a horizontal deflection winding 11 mounted adjacent to a cathode ray tube 10 as well as supplying horizontal rate pulses for various functions within a television receiver. A primary winding 8a of a horizontal output and high voltage transformer 8 receives energy from generator 7. A tertiary winding 8d of transformer 8 supplies retrace pulses to a high voltage multiplier and rectifier assembly 9 which provides a high DC voltage to the ultor terminal of cathode ray tube 10. On the secondary side of transformer 8 there are serially connected an SCR 13, a secondary winding 8b providing horizontal retrace pulses of approximately 80 volts, an inductance 14, an inductance 16, a second secondary winding 8c providing horizontal retrace pulses of approximately 80 volts and a second SCR 17. The anode of SCR 13 and the cathode of SCR 17 are grounded. The junction of inductances 14 and 16 is coupled through a capacitor 15 to ground and also through a vertical deflection winding 18 and a current sampling feedback resistor 19 to ground. The connections from either side of vertical deflection winding 18 to a vertical sawtooth generator 20 provide feedback for purposes to be described in conjunction with FIGS. 3 and 5.

Vertical deflection rate sync pulses 21 also derived from the sync separator are coupled to an input terminal 22 of the vertical sawtooth generator 20 to synchronize the operation thereof. Output signals obtained from vertical sawtooth generator 20 are coupled to a modulator 23. A source of direct current 12 is coupled to horizontal generator 7, vertical sawtooth generator 20 and modulator 23 and supplies operating current thereto.

Horizontal rate pulses obtained from a winding 8e of horizontal transformer 8 are also coupled to modulator 23. Output signals obtained from modulator 23 are coupled through a terminal 24 to the gate electrode of SCR 13 and through output terminal 25 to the gate electrode of SCR 17.

FIGS. 2a-2h illustrate waveforms obtained at various points in the circuit of FIG. 1. In FIG. 2a pulses

30 illustrate horizontal rate retrace pulses such as are obtained at windings 8b, 8c and 8e of horizontal output and high voltage transformer 8. Pulses 31 of FIG. 2b are obtained from modulator 23 and coupled through terminal 24 to the gate electrode of SCR 13 to enable conduction thereof. Pulses 32 of FIG. 2c are coupled through terminal 25 to the gate electrode of SCR 17 to enable conduction thereof. By inspection of FIGS. 2b and 2c, it can be seen that modulator 24 produces output pulses 31 and 32 which have leading edges that vary in time with respect to the leading edges of the retrace pulses 30. The leading edges of pulses 31 are continuously delayed relative to the leading edges of retrace pulses 30 from the beginning until sometime after the center of scan and then ceases. The leading edges of pulses 32 are continuously advanced relative to the leading edges of retrace pulses 30 from sometime before the center until the end of scan.

30 illustrate horizontal rate retrace pulses such as are obtained at windings 8b, 8c and 8e of horizontal output and high voltage transformer 8. Pulses 31 of FIG. 2b are obtained from modulator 23 and coupled through terminal 24 to the gate electrode of SCR 13 to enable conduction thereof. Pulses 32 of FIG. 2c are coupled through terminal 25 to the gate electrode of SCR 17 to enable conduction thereof. By inspection of FIGS. 2b and 2c, it can be seen that modulator 24 produces output pulses 31 and 32 which have leading edges that vary in time with respect to the leading edges of the retrace pulses 30. The leading edges of pulses 31 are continuously delayed relative to the leading edges of retrace pulses 30 from the beginning until sometime after the center of scan and then ceases. The leading edges of pulses 32 are continuously advanced relative to the leading edges of retrace pulses 30 from sometime before the center until the end of scan. The SCR gate control pulses 31 and 32 of FIGS. 2b and 2c associated with the circuit of FIG. 1 are shown to have the same width, with their leading and trailing edges varying in time during the vertical interval relative to the leading edges of the horizontal retrace pulses. Such pulse trains can be generated by any suitable pulse position modulator. Such an equal width pulse train is satisfactory because when SCRs are utilized as switches it is necessary only to gate them on initially, conduction then being controlled only by the forward current through the SCRs.

The leading edges of pulses 31 of FIG. 2b occurring during the first part of the trace interval T O - T 9 enable SCR 13 for conduction. The retrace pulses appearing across winding 8b act as a voltage source positive at the bottom terminal of winding 8b relative to its top terminal which provides conventional current flow from the bottom terminal of winding 8b through inductor 14 and capacitor 15 to ground, and through SCR 13 from its anode to cathode to the negative terminal of transformer winding 8b. This charges capacitor 15 positive w

ith respect to ground. SCR 13 begins to conduct when its gate electrode is forward biased by a pulse 31 and continues to conduct as long as forward current flows in its anode-cathode path.

ith respect to ground. SCR 13 begins to conduct when its gate electrode is forward biased by a pulse 31 and continues to conduct as long as forward current flows in its anode-cathode path. The inductor 14 and capacitor 15 form a series resonant circuit for charging capacitor 15. The slope of the increase and decrease of the current through inductor 14, illustrated by the waveform 33 of FIG. 2d, is determined by the resonant frequency of inductor 14 and capacitor 15.

The resonant frequency of inductor 14 and capacitor 15 as well as that of the circuit comprising inductor 16 and capacitor 15 is chosen to be less than the horizontal deflection frequency to prevent undesirable oscillations. Upon termination of the horizontal retrace pulse the current 33 starts to change at a lesser slope, T 1 - T 2 , than the slope from T 0 - T 1 because winding 8b is no longer a retrace pulse voltage source but a source of opposite polarity trace voltage and the transformed inductance is greater during trace which decreases the resonant circuit frequency. SCR 13 turns off when the current of waveform 33 reaches zero, such as at T 2 . At this time, the voltage across capacitor 15 has reached its maximum as indicated by waveform 35 of FIG. 2f. At the horizontal rate, the inductance of vertical deflection winding 18 which is in parallel with capacitor 15 is so large that it has little effect on the above-described resonant charging circuits for capacitor 15.

Deflection current is obtained by discharging capacitor 15 via winding 18 which integrates the horizontal rate voltage across capacitor 15 to a substantially sawtooth current at the vertical rate. Although th

e voltage 35 is shown as returning to ground at the beginning of the gate pulses, the voltage 35 actually returns to a voltage value slightly above or below ground, depending on the resonance of winding 18 because during T 2 - T 4 the parallel connection of capacitor 15 and winding 18 is disconnected from the rest of the circuit. However, as shown in more detail in FIG. 3, the DC feedback stabilizes the operating point of the deflection circuit and the AC feedback controls amplitude and linearity of the deflection circuit. Deflection winding 18 provides a discharge path across capacitor 15. Due to the large inductance of winding 18, the discharge current cannot follow the triangular voltage across capacitor 15. Consequently, the current through winding 18 averages the voltage across capacitor 15. Therefore, winding 18 acts as a current sink to discharge capacitor 15, resulting that voltage 35 decreases linearly during the interval T 2 - T 4 , etc. The parallel resonant frequency of capacitor 15 and vertical deflection winding 18 also determines the vertical retrace interval. The discharge current of capacitor 15 through winding 18 represents the integral of the voltage waveform 35 and as a result of which integration the current through winding 18 is slightly parabolic in shape at the horizontal rate as illustrated in FIG. 2g showing the deflection current 36. Assuming a fixed inductance of winding 18 the amplitude of the parabolic component is inversely proportional to the value of capacitor 15.

e voltage 35 is shown as returning to ground at the beginning of the gate pulses, the voltage 35 actually returns to a voltage value slightly above or below ground, depending on the resonance of winding 18 because during T 2 - T 4 the parallel connection of capacitor 15 and winding 18 is disconnected from the rest of the circuit. However, as shown in more detail in FIG. 3, the DC feedback stabilizes the operating point of the deflection circuit and the AC feedback controls amplitude and linearity of the deflection circuit. Deflection winding 18 provides a discharge path across capacitor 15. Due to the large inductance of winding 18, the discharge current cannot follow the triangular voltage across capacitor 15. Consequently, the current through winding 18 averages the voltage across capacitor 15. Therefore, winding 18 acts as a current sink to discharge capacitor 15, resulting that voltage 35 decreases linearly during the interval T 2 - T 4 , etc. The parallel resonant frequency of capacitor 15 and vertical deflection winding 18 also determines the vertical retrace interval. The discharge current of capacitor 15 through winding 18 represents the integral of the voltage waveform 35 and as a result of which integration the current through winding 18 is slightly parabolic in shape at the horizontal rate as illustrated in FIG. 2g showing the deflection current 36. Assuming a fixed inductance of winding 18 the amplitude of the parabolic component is inversely proportional to the value of capacitor 15. As the vertical deflection interval proceeds, modulator 23 produces pulses 31 for SCR 13 which have leading edges increasingly delayed in time relative to the leading edges of the horizontal retrace pulses 30. Hence the conduction time of SCR 13 begins later and later from the beginning of each horizontal retrace pulse 30 of FIG. 2a. This results in a decreasing charging current through inductor 14 and a decreasing voltage 35 across capacitor 15. It follows that the current through deflection winding 18 likewise decreases. Current waveform 36 crosses over the zero axis at T 7 .

Prior to

this time modulator 23 started producing pulses 32 to enable conduction of SCR 17. A gating pulse 32 starting slightly after T 6 is coupled through terminal 25 to enable conduction of SCR 17. SCR 17 conducts from its anode to cathode to ground up through capacitor 15 through inductance 16 to the top terminal of winding 8c which has a negative polarity retrace pulse relative to its bottom terminal. Hence, conduction of SCR 17 charges capacitor 15 in a direction to place a negative charge across capacitor 15 relative to ground. Since SCR 17 conducts longer than SCR 13 as determined by the respective enabling pulses 32 and 31 during the time beginning at T 8 , the net charge on capacitor 15 now becomes negative.

this time modulator 23 started producing pulses 32 to enable conduction of SCR 17. A gating pulse 32 starting slightly after T 6 is coupled through terminal 25 to enable conduction of SCR 17. SCR 17 conducts from its anode to cathode to ground up through capacitor 15 through inductance 16 to the top terminal of winding 8c which has a negative polarity retrace pulse relative to its bottom terminal. Hence, conduction of SCR 17 charges capacitor 15 in a direction to place a negative charge across capacitor 15 relative to ground. Since SCR 17 conducts longer than SCR 13 as determined by the respective enabling pulses 32 and 31 during the time beginning at T 8 , the net charge on capacitor 15 now becomes negative. During the period when both SCRs 13 and 17 conduct, generally around T 6 - T 9 , only the difference between the positive and negative currents 33 and 34 will charge capacitor 15. The remainder of the two currents circulate in a quiescent path comprising SCR 13, winding 8b, inductance 14, inductance 16, winding 8c and SCR 17.

The charging current through inductance 16 for capacitor 15 as illustrated by waveform 34 in FIG. 2e increases for the remainder of the vertical trace interval ending at T 11 . Thus, the negative voltage excursions across capacitor 15 increase during this interval and likewise the negative current through deflection winding 18 as illustrated by waveform 36 of FIG. 2g.

FIG. 2h illustrates the voltage acros SCR 13 during the vertical deflection cycle. During T 0 - T 2 SCR 13 conducts the retrace pulse current and the current stored in inductor 14 and winding 8b at the end of the retrace pulse at T 1 . T 2 - T 3 of waveform represents the SCR recovery time when current waveform 33 is zero and the voltage waveform 35 is decreasing from a peak. During T 3 - T 4 a negative portion of the retrace pulse appears across SCR 13 as it is not yet switched on. At T 4 , waveform 31 gates SCR 13 on and it again conducts. It is to be understood that the voltage waveform acros SCR 17 would be a mirror image waveform of opposite polarity of waveform 37.

In FIGS. 2d and 2e, overlapping charging currents are shown for only two periods of SCR gating pulses 31 and 32. Since there are about 262 horizontal retrace pulses during each complete vertical deflection cycle, T 0 - T 0 ', actually there may be many overlapping portions of charging currents 33 and 34. Thus, crossover is very smoothly and linearly achieved because the difference between currents 33 and 34 decreases to zero at the crossover point. Due to the reactive elements in the circuit, such as capacitor 15, crossover may actually be shifted a slight amount from point T 7 indicated in deflection yoke winding current waveform 36.

Vertical retrace is obtained by one-half cycle of the free ringing parallel resonant circuit formed by capacitor 15 and winding 18. By this, the voltage across winding 18 and the magnetic field in winding 18 change their polarity.

It is noted that there are no charging currents during the vertical retrace interval T 11 - T 0 ' except for a single charging cycle through SCR 13 and inductance 14, which charging cycle initiates the vertical retrace interval. This is because modulator 23 responds to the waveforms coupled from vertical sawtooth generator 20 to inhibit the gating pulses at terminal 25 which would normally enable SCR 17 to conduct and initiates gating pulses at terminal 24. SCR 13 will conduct heavily and causes the rapid change of voltage polarity across capacitor 15. Then, the vertical retrace pulse shown in waveform 35 during T 11 - T 0 ' reverse biases SCR 13 and prevents it from conducting during the remainder of the vertical retrace interval.

Significant power dissipation reduction is achieved in the circuit of FIG. 1 because SCRs 13 and 17 are operated as switches, i.e., either nonconducting or saturated. Hence, little power is dissipated in the devices. Further, no external direct current power supply is required to operate the SCRs 13 and 17. The energy sources for the SCRs are the horizontal retrace pulses appearing across windings 8b and 8c. This results in a further power consumption reduction in that no rectifier and filter networks with their attendant power consumption are required for operation of the circuit.

The loading of the horizontal deflection circuit by the vertical deflection circuit during each horizontal retrace period results in at least some side pincushion correction because the current drain (loading) is greatest at the beginning and end of the vertical trace interval and decreases to a minimum at the center of the vertical trace interval. At least some to

p and bottom pincushion correction is also provided with no additional circuitry by virtue of the parabolic modulation of the vertical deflection current at a horizontal rate caused by the integration of the voltage across capacitor 15 by the inductance of deflection winding 18. This parabolic component is greatest at the beginning and end of the vertical trace interval and diminishes toward the center of the vertical trace interval providing the commonly referred to "bow tie" modulation for effecting top and bottom pincushion correction of the scanned raster. This is clearly illustrated by deflection winding 18 voltage waveform 27 of FIG. 1.

p and bottom pincushion correction is also provided with no additional circuitry by virtue of the parabolic modulation of the vertical deflection current at a horizontal rate caused by the integration of the voltage across capacitor 15 by the inductance of deflection winding 18. This parabolic component is greatest at the beginning and end of the vertical trace interval and diminishes toward the center of the vertical trace interval providing the commonly referred to "bow tie" modulation for effecting top and bottom pincushion correction of the scanned raster. This is clearly illustrated by deflection winding 18 voltage waveform 27 of FIG. 1. FIG. 3 is a block and schematic diagram showing in more detail a switched vertical deflection system similar to that shown in FIG. 1. A source of vertical sync pulses 21 is coupled to a terminal 22 of a transistor 40. The emitter of transistor 40 is grounded and its collector electrode is coupled through a diode 41, a resistor 42, a potentiometer 44 serving as a height control, and a resistor 45 to a source of positive potential B+ obtained from DC supply 12. B+ may be in the order of 24 volts. The junction of resistors 42 and 44 is coupled through a first capacitor 43, a second capacitor 48, a resistor 49, a resistor 50 and a potentiometer 51 serving as a linearity control to ground. The junction of capacitors 43 and 48 is coupled through a resistor 46 to an inverting terminal of an amplifier 47. A resistor 52 couples the inverting terminal of amplifier 47 to a centering potentiometer 53 which in turn is connected through a resistor 54 to B+. Coupled across the inverting input terminal and the output terminal of amplifier 47 are two back-to-back zener diodes 60 and 61 for limiting the peak excursion of the signals. A resistor 59 provides feedback for the amplifier, and series coupled resistor 57 and capacitor 58 in parallel with capacitor 56 serve a damping function to prevent undesirable oscillation or ringing in amplifier 47. Series coupled resistors 63 and 64 between B+ and ground form a DC voltage divider for developing a reference voltage which is coupled through a resistor 62 to the non-inverting input terminal of amplifier 47 and through a resistor 65 to the non-inverting terminal of a second amplifier 66. The output terminal of amplifier 47 is coupled through a resistor 67 to the inverting input terminal of amplifier 66. A resistor 68 coupled from the output terminal of amplifier 66 to its inverting input terminal provides feedback for the amplifier.

The output terminal of amplifier 47 is coupled through a diode 71 to the base electrode of a first transistor 72 of a differential amplifier 73. Differential amplifier 73 performs a pulse width modulation function to be described subsequently. The collector of transistor 72 is grounded and the emitter electrode of transistors 72 and 74 are coupled through a common emitter resistor 75 to B+. Biasing resistors 76 and 77 are coupled from the common emitter junction to the respective bases of transistors 72 and 74. The collector electrode of transistor 74 provides an output signal which is coupled through a diode 93 to the base of a driver transistor 94. The base electrode of transistor 74 is coupled through a diode 78 to the emitter of a transistor 112 and through a diode 86 to the base electrode of a transistor 82 which forms a part of a second differential amplifier 81 which also acts as a pulse width modulator to be described subsequently. The emitters of transistor 82 and transistor 80 are coupled through a common resistor 83 to B+. Biasing resistors 84 and 85, respectively, are coupled from the emitters of transistors 80 and 82 to their bases. The base of transistor 80 is coupled through a diode 79 to the output terminal of amplifier 66. The collector electrode of transistor 82 is coupled to the base of a second driver transistor 87.

Driver transistor 87 has its collector coupled through a resistor 90 to the B+ supply. Resistor 91 and capacitor 92 serve to decouple this stage from the B+ supply. The emitter of transistor 87 is coupled through a resistor 89 to ground and to the gate electrode of an SCR 17.

Driver transistor 94 has its collector electrode coupled through a diode 97 and a resistor 98 to the B+ supply. The emitter electrode of transistor 94 is coupled to the gate electrode of an SCR 13 and through a resistor 96 to the junction of a vertical deflection winding 18 and a capacitor 15. The other terminal of capacitor 15 is grounded and the other terminal of deflection winding 18 is coupled through a current sampling feedback resistor 19 to ground. DC signal obtained from the top of vertical deflection winding 18 is coupled through a series resistor 115 and a shunt capacitor 116 to a terminal of potentiometer 53 to be fed back to amplifier 47. This DC feedback sets the operating point of the DC coupled vertical deflection circuit. An AC feedback path is coupled from the junction of vertical deflection winding 18 and feedback resistor 19 through a capacitor 114 to the junction of resistors 49 and 50. This feedback path serves to provide linearity correction in conjunction with the setting of linearity potentiometer 51.

The output stages including SCRs 13 and 17 and high voltage and output transformer 8 are similar to those described in conjunction with FIG. 1.

A winding 8e of transformer 8 is coupled through a voltage divider comprising resistor 101 and resistor 102 to ground. The junction of resistors 101 and 102 provides horizontal rate retrace pulses at the base of a transistor amplifier 103. The emitter of transistor 103 is grounded and its collector is coupled through a load resistor 104 to B+. The collector of transistor 103 is coupled to the base of a transistor 105 to provide drive current thereto. The emitter of transistor 105 is grounded and its collector is coupled through a resistor 106 to B+ and to the base of transistor 107. The emitter of transistor 107 is grounded and its collector is coupled through a resistor 108 to B+ and through a capacitor 109 and a diode 110 poled as indicated to ground. A resistor 111 is coupled to the collector of transistor 105 and the junction between capacitor 109 and resistor 110.

The collector transistor 107 is further coupled to the base of a transistor 112 connected in circuit as an emitter-follower stage. The collector of transistor 112 is grounded and its emitter is coupled through a resistor 113 to B+. Generally, transistors 103, 105, 107 and 112 and their associated circuitry function to provide sawtooth signals at the horizontal deflection rate which are coupled through diodes 78 and 86 to one input terminal of each of diferential amplifier 73 and 81, respectively. The base of transistor 112 is coupled to the collector of transistor 107 through series connected resistor 130 and potentiometer 131 to ground. Potentiometer 131 provides for overlapping operation of SCR 13 and SCR 17.

During operation, the positive going vertical sync pulses coupled to the base of transistor 40 c

ause it to conduct which discharges the sawtooth charging capacitors 43 and 48. To begin the vertical trace interval at the termination of vertical sync pulse 22, transistor 40 is cut off and capacitors 43 and 48 charge through a path from the B+ supply through resistor 45, potentiometer 44, resistor 49, capacitor 114 and resistor 19 to ground. The sawtooth wave is coupled through resistor 46 to amplifier 47 and any difference between it and the sawtooth waveform fed back through capacitor 114 appears inverted at the output terminal of amplifier 47, as illustrated by the error signal which is indicated as a vertical rate negative going sawtooth wave form 69. Adjustment of the centering potentiometer 53 varies the DC level of the sawtooth waveform at the input of amplifier 47 and because of the direct current coupling to the deflection winding 18 provides a DC component to achieve centering of the raster by adding a DC component to the deflection yoke current. Additionally, the DC feedback from the top of winding 18 through resistor 115 to one side of centering potentiometer 53 provides stability of the DC operating point.

ause it to conduct which discharges the sawtooth charging capacitors 43 and 48. To begin the vertical trace interval at the termination of vertical sync pulse 22, transistor 40 is cut off and capacitors 43 and 48 charge through a path from the B+ supply through resistor 45, potentiometer 44, resistor 49, capacitor 114 and resistor 19 to ground. The sawtooth wave is coupled through resistor 46 to amplifier 47 and any difference between it and the sawtooth waveform fed back through capacitor 114 appears inverted at the output terminal of amplifier 47, as illustrated by the error signal which is indicated as a vertical rate negative going sawtooth wave form 69. Adjustment of the centering potentiometer 53 varies the DC level of the sawtooth waveform at the input of amplifier 47 and because of the direct current coupling to the deflection winding 18 provides a DC component to achieve centering of the raster by adding a DC component to the deflection yoke current. Additionally, the DC feedback from the top of winding 18 through resistor 115 to one side of centering potentiometer 53 provides stability of the DC operating point. The negative going sawtooth waveform 69 obtained at the output terminal of amplifier 47 is coupled to the inverting terminal of amplifier 66 which provides at its output terminal an error signal which is illustrated as a positive going vertical rate sawtooth waveform 70 with the same but opposite polarity level as the DC level of waveform 69, referring to the reference voltage established at the junction of resistors 63 and 64. The opposite polarity vertical rate sawtooth waveforms 69 and 70 are coupled through diodes 71 and 79, respectively, to form the other input of respective differential amplifiers 73 and 81.

FI

GS. 4a -4c illustrate waveforms obtained at various points in the circuit of FIG. 3. Waveform 69 of FIG. 4a is a portion of the negative going sawtooth error waveform applied to the base electrode of transistor 72 of differential amplifier 73. Waveform 70 of FIG. 4a is a portion of the positive going vertical rate sawtooth error waveform coupled to the base electrode of transistor 80 of differential amplifier 81.

GS. 4a -4c illustrate waveforms obtained at various points in the circuit of FIG. 3. Waveform 69 of FIG. 4a is a portion of the negative going sawtooth error waveform applied to the base electrode of transistor 72 of differential amplifier 73. Waveform 70 of FIG. 4a is a portion of the positive going vertical rate sawtooth error waveform coupled to the base electrode of transistor 80 of differential amplifier 81. The positive going horizontal retrace pulses coupled to the base of transistor 103 cause it to conduct and the inverted retrace pulses are coupled to the base of transistor 105 which cuts off during the horizontal retrace interval. The positive rise of voltage at the collector of transistor 105 causes transistor 107 to conduct. The positive charge on the right hand side of capacitor 109, which had previously been established by the voltage divider comprising resistors 108, 130 and potentiometer 130 connected between B+ and ground is suddenly lowered by the conduction of transistor 107 and the drop appears as a negative voltage at the junction between capacitor 109 and diode 110. The current which was previously flowing through resistor 106 and transistor 105 now divides between the base-emitter junction of transistor 107 and through resistor 111 to the negative side of capacitor 109. Thus, capacitor 109 now starts to discharge through transistor 107 to ground, through the B+ source, through current source resistor 106, through resistor 111 to the left (negative) terminal of capacitor 109. In this circuit, which is a modified type of Miller integrator, the current through resistor 111 equals the current through resistor 106, except for the very small amount of current flowing through the base of transistor 107. Resistor 111 has a constant voltage drop across it and provides the negative going step of waveform 120. The constant current discharge of capacitor 109 through transistor 107 provides a negative going sawtooth voltage waveform at the collector of transistor 107 as illustrated by waveform 120 of FIG. 4a. Transistor 112 is connected as an emitter follower and the voltage at its emitter is the waveform 120 of FIG. 4a. The most positive portion of waveform 120 is determined by the setting of potentiometer 131 in the voltage divider network. The sharp negative going drop in waveform 120 is caused by the voltage drop across resistor 111 caused by the current through resistor 106. The abrupt positive going portion of waveform 120 is caused by the termination of the retrace pulses appearing at the base of transistor 103, which causes it to cut off, transistor 105 to conduct and transistor 107 to cut off, bringing the base voltage of transistor 112 and hence the voltage of waveform 120 up to the level determined by the setting of potentiometer 131, to which level capacitor 109 charges from B+ through resistor 108 and diode 110 to ground.

The negative going pulses 120 with negative going sawtooth tips obtained at the emitter of transistor 112 are coupled through diodes 78 and 86 to the bases of transistors 74 and 82, respectively. With regard to differential amplifier 73, the one of transistors 72 and 74 which has the most negative voltage at its base will conduct and the other transistor will cut off. Thus, during the first part of the vertical trace interval when vertical rate waveform 69 of FIG. 4a is positive relative to the negative going sawtooth waveform 120, transistor 74 will conduct, saturating and providing a series of positive going pulses at the horizontal rate at its collector through diode 93 and transistor driver 94 to cause SCR 13 to conduct. The drive pulses at the gate electrode of SCR 13 are illustrated by the pulses 123 of FIG. 4b. In FIGS. 4a and 4b, it can be seen that as the waveform 69 becomes more negative the pulses 123 become shorter and shorter. With reference to FIGS. 4a and 4b, it can be seen that the waveform 120 causes transistor 74 to conduct at the horizontal rate as long as the negative going sawtooth portion of voltage waveform 120 is more negative than the level of vertical rate waveform 69, thus producing drive pulses for enabling conduction of SCR 13 and charging capacitor 15 at a horizontal rate with a substantially linearly decreasing positive current.

At the time interval T 4 the horizontal rate sawtooth portion of waveform 120 becomes more negative relative to the positive going vertical rate sawtooth error waveform 70 and transistor 82 will begin to conduct during each horizontal retrace period with the leading edge of its collector voltage increasingly approaching the leading edge of the waveform 120 as the vertical interval progresses as illustrated by the waveform 124 of FIG. 4c. These positive pulses of waveform 124 are coupled through driver transistor 87 and cause SCR 17 to conduct. Current flowing from ground up through capacitor 15 through inductor 16 to the bottom terminal of winding 8c, which has a negative retrace pulse relative to its top terminal and through SCR 17 provides an increasing negative voltage to be developed across capacitor 15 during the latter half of the vertical trace interval.

Referring to FIGS. 4b and 4c, it can be seen that the pulses of waveforms 123 and 124 overlap for an interval around the center of the vertical trace interval. At T 6 , equal conduction of SCRs 13 and 17 occurs, leaving a net charging current of zero into capacitor 15. This is the crossover point. As previously described, the setting of potentiometer 131 determines the voltage level on which pulses 120 are superimposed and, hence, the number of overlapping pulses of waveforms 123 and 124. It can be seen that the positive and negative currents respectively dominate to create the sawtooth current through deflection winding 18 on the le

ft and right sides, respectively, of T 6 . The reference voltage V R shown as centerline in FIG. 4a represents the nominal average DC voltage of the sawtooth waveforms 69 and 70. This reference voltage is determined by the voltage divider formed by resistors 63 and 64 shown in FIG. 3. The setting of the centering control potentiometer 53 causes by virtue of the amplifiers 47 and 66 that the voltage waveforms 69 and 70 shift in opposite polarity directions with reference to V R . This causes the crossover point of waveforms 69 and 70 of FIG. 4a to move in either direction from the center as shown, resulting that the deflection current through winding 18 superimposes on a DC centering current depending upon the setting of potentiometer 53.

ft and right sides, respectively, of T 6 . The reference voltage V R shown as centerline in FIG. 4a represents the nominal average DC voltage of the sawtooth waveforms 69 and 70. This reference voltage is determined by the voltage divider formed by resistors 63 and 64 shown in FIG. 3. The setting of the centering control potentiometer 53 causes by virtue of the amplifiers 47 and 66 that the voltage waveforms 69 and 70 shift in opposite polarity directions with reference to V R . This causes the crossover point of waveforms 69 and 70 of FIG. 4a to move in either direction from the center as shown, resulting that the deflection current through winding 18 superimposes on a DC centering current depending upon the setting of potentiometer 53. Retrace is initiated by the conduction of transistor 40 which causes the negative pulse portion of vertical rate waveform 70 coupled to the base electrode of transistor 80 of differential amplifier 81 to cause transistor 82 to stop conducting and to stop producing pulses 124. At the same time the positive going portion of waveform 69 coupled to transistor 72 of differential amplifier 73 cuts off transistor 72 and leaves transistor 74 enabled for conduction when the negative going sawtooth w

aveform 120 at the horizontal rate is applied to its base. The first horizontal sawtooth 120 appearing at this time generates a wide pulse 123 at the collector of transistor 74 and gates SCR 13 to conduct at a very early time with reference to the horizontal retrace pulses 30 of FIG. 2a. The current through SCR 13 charges capacitor 15 positive and the magnetic energy stored in the deflection winding 18 causes the voltage across capacitor 15 to rise further positive. This is illustrated in FIGS. 2b, 2d, 2f and 2g. The retrace pulse time of voltage waveform 35 of FIG. 2f is approximately three to four horizontal lines. The positive going retrace pulse is coupled through biasing resistor 95 to the cathode of diode 93 to reverse bias it with relation to the relatively low level positive going pulses produced at its anode as transistor 74 conducts. Similarly, diode 97 is reverse biased during the vertical retrace interval and disconnects transistor 94 from the B+ supply, allowing the retrace pulse to rise above the B+ level for one-half the cycle determined by the resonant frequency of the parallel combination of capacitor 15 and deflection winding 18. Since the deflection winding is not clamped to any voltage during the retrace interval, the retrace pulse voltage can rise to a relatively high level, causing a quick reversal of deflection winding current and, hence, a short retrace interval. After one-half cycle of resonance the vertical retrace pulse begins to swing negative, forward biasing diodes 93 and 97 and permits gate pulses to be applied to SCR 13, enabling a new trace interval to begin.

aveform 120 at the horizontal rate is applied to its base. The first horizontal sawtooth 120 appearing at this time generates a wide pulse 123 at the collector of transistor 74 and gates SCR 13 to conduct at a very early time with reference to the horizontal retrace pulses 30 of FIG. 2a. The current through SCR 13 charges capacitor 15 positive and the magnetic energy stored in the deflection winding 18 causes the voltage across capacitor 15 to rise further positive. This is illustrated in FIGS. 2b, 2d, 2f and 2g. The retrace pulse time of voltage waveform 35 of FIG. 2f is approximately three to four horizontal lines. The positive going retrace pulse is coupled through biasing resistor 95 to the cathode of diode 93 to reverse bias it with relation to the relatively low level positive going pulses produced at its anode as transistor 74 conducts. Similarly, diode 97 is reverse biased during the vertical retrace interval and disconnects transistor 94 from the B+ supply, allowing the retrace pulse to rise above the B+ level for one-half the cycle determined by the resonant frequency of the parallel combination of capacitor 15 and deflection winding 18. Since the deflection winding is not clamped to any voltage during the retrace interval, the retrace pulse voltage can rise to a relatively high level, causing a quick reversal of deflection winding current and, hence, a short retrace interval. After one-half cycle of resonance the vertical retrace pulse begins to swing negative, forward biasing diodes 93 and 97 and permits gate pulses to be applied to SCR 13, enabling a new trace interval to begin. In FIG. 3 the cathode of SCR 13 is connected to capacitor 15 instead of the top of winding 8b as in FIG. 1. Thus, in the arrangement of FIG. 3, the cathode and gate electrodes are floating at a much lower voltage than in FIG. 1, resulting in greater stability in the operation of SCR 13.

In FIG. 3, unlike FIG. 1, a pulse width modulator arrangement is utilized to control the conduction of SCRs 13 and 17 with the leading edge only of the pulses of waveforms 123 and 124 being varied relative to the leading edges of the horizontal retrace pulses.

FIG.

5 is a detailed block and schematic circuit diagram of another switched vertical system embodying the invention. The essential difference between the embodiments of FIG. 5 and FIG. 3 is that in FIG. 5 a separate oscillator and sawtooth generator 150 produces a stable sawtooth voltage waveform obtained from an output terminal of an amplifier 176, which waveform is coupled to amplifiers 47 and 66 and the rest of the vertical generator which acts as a linear amplifier, feedback being coupled from the deflection winding 18 to amplifier 47. An advantage of the FIG. 5 embodiment is that interlace of two successive vertical fields is readily accomplished.

5 is a detailed block and schematic circuit diagram of another switched vertical system embodying the invention. The essential difference between the embodiments of FIG. 5 and FIG. 3 is that in FIG. 5 a separate oscillator and sawtooth generator 150 produces a stable sawtooth voltage waveform obtained from an output terminal of an amplifier 176, which waveform is coupled to amplifiers 47 and 66 and the rest of the vertical generator which acts as a linear amplifier, feedback being coupled from the deflection winding 18 to amplifier 47. An advantage of the FIG. 5 embodiment is that interlace of two successive vertical fields is readily accomplished. A vertical sync pulse 21 is coupled to a terminal 22 and through a resistor 151, a diode 153, a capacitor 155 and a diode 156 to cause transistor 157 to conduct to start the retrace interval. The conduction path of transistor 157 is from the B+ supply through resistor 169 to ground. The drop in potential at the collector of transistor 157 is coupled through diode 158 and resistor 159 to cause transistor 160 to conduct. Transistor 160 conducting discharges sawtooth generating capacitors 174 and 175 through a resistor 172. The emitter-collector current path is completed by the path from B+ through height control potentiometer 171, resistor 170, resistor 172 and resistor 173 to ground. Conduction of transistor 160 during the vertical retrace interval causes a negative going retrace voltage waveform portion to be generated at the inverting input terminal of amplifier 176.

The lowered collector voltage of transistor 157 following the leading edge of sync pulses 21 is coupled through a resistor 161 to cause transistor 162 to conduct. The main conduction path of transistor 162 is from the B+ terminal through resistor 165, resistor 164 and resistor 154 to ground, resistor 154 being in parallel with the series connection of capacitor 155, diode 156 and the base-emitter junction of transistor 157 to ground. This current path allows capacitor 155 to discharge through diode 156 and the base-emitter junction of transistor 157. When capacitor 155 has discharged to a point that diode 156 and the base-emitter junction of transistor 157 are no longer forward biased, transistor 157, transistor 160 and transistor 162 will cut off. At this time capacitors 174 and 175 start forming a sawtooth voltage waveform at their junction by charging from the B+ supply through potentiometer 171, resistor 170 and resistor 173 to ground, forming a negative going sawtooth wave at the output terminal of amplifier 176. At the same time, capacitor 155 starts charging through potentiometer 168 which serves as a hold control, resistor 167 and resistor 154 to ground to determine the free-running frequency of the oscillator portion comprising transistors 162 and 157. In the absence of incoming vertical sync pulses 21, transistor 157 would conduct and initiate vertical retrace when the charge across capacitor 155 became positive enough to forward bias diode 156 and transistor 157. Capacitor 166 coupled from the junction of resistors 164 and 165 to ground serves to decouple the power supply. Capacitor 152 coupled from the junction of resistor 151 and diode 153 to ground serves to decouple any horizontal rate energy from being passed through diode 153.

Resistors 182 and 183 coupled between B+ and ground have their junction coupled to the non-inverting terminal of an amplifier 185 for producing a stable reference voltage at the output terminal of amplifier 185. Capacitor 184 decouples any voltage variations from reaching the non-inverting input terminal of amplifier 185. The output terminal of amplifier 185 is coupled back to its inverting input terminal for feedback purposes and is also coupled through a resistor 177 to supply the reference voltage to the non-inverting input terminal of amplifier 176.

A potentiometer 178 and resistor 1