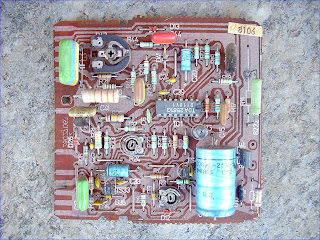

The system is developed on one big board carrying all functions except timer and frontend sections.

Furthermore it has a programmable realtime digital clock which allows to start the tellye at a prefixed time on a prefixed program and prefixed day of the week with even separated and dedicated Ucontroller for timer and displays.

FURTHERMORE The PHILIPS CHASSIS K12z WAS the first PHILIPS monocarrier type chassis with isolated from mains circuits. Previous K12 was direct mains supply type.

The PHILIPS chassis K12z is using the 30AX system crt tube family instead of the 20 AX originally used.

The chassis is a pretty unique type because it was introducing improvements and technology philosophy kindly singular and unique in it's fashion.

From signal processing to Video Matrixing to power supply technology and many further aspects this chassis was a reference to understand PHILIPS development flexibility.

This chassis has known many further versioning and enhancements even in more sophisticated and complex types with different CRT TUBE like the 30AX FAMILY.

Modularity is the main concept of construction but some Units like the E/W and FRAME UNIT gave problems in the insertion slot which often was burning the contacts producing several faults.

The solution was simple: A complete hardening with soldering and reworking of the enpoints of the Units contacts was a definitive solution for long time. But when the damage was more extended the only solution was to direct wire all contacts from Unit to chassis !

Line Deflection + EHT, Line synchronized Supply, EW Correction + Supply, Frame Deflection, Signal Section Parts.

PHILIPS 26CP2402/08R CHASSIS K12Z CIRCUIT ARRANGEMENT IN A PICTURE DISPLAY DEVICE UTILIZING A STABILIZED SUPPLY VOLTAGE CIRCUIT:

Line synch Switched Mode Power Supply with Line deflection output Transistor Drive Circuit:

A stabilized supply voltage circuit for a picture display device comprising a chopper wherein the switching signal has the line frequency and is duration-modulated. The coil of the chopper constitutes the primary winding of a transformer a secondary winding of which drives the line output transistor so that the switching transistor of the chopper also functions as a driver for the line output stage. The oscillator generating the switching signal may be the line oscillator. In a special embodiment the driver and line output transistor conduct simultaneously and in order to limit the base current of the line output transistor a coil shunted by a diode is incorporated in the drive line of the line output transistor. Other secondary windings of the transformer drive diodes which conduct simultaneously with the efficiency diode of the chopper so as to generate further stabilized supply voltages.

Description:

Such a circuit arrangement is known from German "Auslegeschrift" 1.293.304. wherein a circuit arrangement is described which has for its object to convert an input direct voltage which is generated between two terminals into a different direct voltage. The circuit emp

loys a switch connected to the first terminal of the input voltage and periodically opens and closes so that the input voltage is converted into a pulsatory voltage. This pulsatory voltage is then applied to a coil. A diode is arranged between the junction of the switch and the coil and the second terminal of the input voltage whilst a load and a charge capacitor in parallel thereto are arranged between the other end of the coil and the second terminal of the input voltage. The assembly operates in accordance with the known efficiency principle i.e., the current supplied to the load flows alternately through the switch and through the diode. The function of the switch is performed by a switching transistor which is driven by a periodical pulsatory voltage which saturates this transistor for a given part of the period. Such a configuration is known under different names in the literature; it will be referred to herein as a "chopper." A known advantage thereof, is that the switching transistor must be able to stand a high voltage or provide a great current but it need not dissipate a great power. The output voltage of the chopper is compared with a constant reference voltage. If the output voltage attempts to vary because the input voltage and/or the load varies, a voltage causing a duration modulation of the pulses is produced at the output of the comparison arrangement. As a result the quantity of the energy stored in the coil varies and the output voltage is maintained constant. In the German "Auslegeschrift" referred to it is therefore an object to provide a stabilized supply

voltage device.

In the circuit arrangement according to the mentioned German "Auslegeschrift" the frequency of the load variations or a harmonic thereof is chosen as the frequency for the switching voltage. Particularly when the load fed by the chopper is the line deflection circuit of a picture display device, wherein thus the impedance of the load varies in the rhythm of the line frequency, the frequency of the switching voltage is equal to or is a multiple of the line frequency.

It is to be noted that the chopper need not necessarily be formed as that in the mentioned German "Auslegeschrift." In fact, it is known from literature that the efficiency diode and the coil may be exchanged. It is alternatively possible for the coil to be provided at the first terminal of the input voltage whilst the switching transistor is arranged between the other end and the second terminal of the input voltage. The efficiency diode is then provided between the junction of said end and the switching transistor and the load. It may be recognized that for all these modifications a voltage is present across the connections of the coil which voltage has the same frequency and the same shape as the pulsatory switching voltage. The control voltage of a line deflection circuit is a pulsatory voltage which causes the line output transistor to be saturates and cut off alternately. The invention is based on the recognition that the voltage present across the connections of the coil is suitable to function as such a control voltage and that the coil constitutes the primary of a transformer. To this end the circuit arrangement according to the invention is characterized in that a secondary winding of the transformer drives the switching element which applies a line deflection current to line deflection coils and by which the voltage for the final anode of a picture display tube which forms part of the picture display device is generated, and that the ratio between the period during which the switching transistor is saturated and the entire period, i.e., the switching transistor duty cycle is between 0.3 and 0.7 during normal operation.

The invention is also based on the recognition that the duration modulation which is necessary to stabilize the supply voltage with the switching transistor does not exert influence on the driving of the line output transistor. This resides in the fact that in case of a longer or shorter cut-off period of the line output transistor the current flowing through the line deflection coils thereof is not influenced because of the efficiency diode current and transistor current are taken over or, in case of a special kind of transistor, the collector-emitter current is taken over by the base collector current and conversely. However, in that case the above-mentioned ratios of 0.3 : 0.7 should be taken into account since otherwise this take-over principle is jeopardized.

As will be further explained the use of the switching transistor as a driver for the line output transistor in an embodiment to be especially described hereinafter has the further advantage that the line output transistor automatically becomes non-conductive when this switching transistor is short circuited so that the deflection and the EHT for the display tube drop out and thus avoid damage thereof.

As will be further explained the use of the switching transistor as a driver for the line output transistor in an embodiment to be especially described hereinafter has the further advantage that the line output transistor automatically becomes non-conductive when this switching transistor is short circuited so that the deflection and the EHT for the display tube drop out and thus avoid damage thereof. Due to the step according to the invention the switching transistor in the stabilized supply functions as a driver for the line deflection circuit. The circuit arrangement according to the invention may in addition be equipped with a very efficient safety circuit so that the reliability is considerably enhanced, which is described in the U.S. Pat. No. 3,629,686. The invention is furthermore based on the recognition of the fact that the pulsatory voltage present across the connections of the coil is furthermore used and to this end the circuit arrangement according to the invention is characterized in that secondary windings of the transformer drive diodes which conduct simultaneously with the efficiency diode so as to generate further stabilized direct voltages, one end of said diodes being connected to ground.

Due to the step according to the invention the switching transistor in the stabilized supply functions as a driver for the line deflection circuit. The circuit arrangement according to the invention may in addition be equipped with a very efficient safety circuit so that the reliability is considerably enhanced, which is described in the U.S. Pat. No. 3,629,686. The invention is furthermore based on the recognition of the fact that the pulsatory voltage present across the connections of the coil is furthermore used and to this end the circuit arrangement according to the invention is characterized in that secondary windings of the transformer drive diodes which conduct simultaneously with the efficiency diode so as to generate further stabilized direct voltages, one end of said diodes being connected to ground.In order that the invention may be readily carried into effect, a few embodiments thereof will now be described in detail by way of example with reference to the accompanying diagrammatic drawings in which:

FIG. 1 shows a principle circuit diagram wherein the chopper and the line deflection circuit are further shown but other circuits are not further shown.

FIGS. 2a, 2b and 2c show the variation as a function of time of two currents and of a voltage occurring in the circuit arrangement according to FIG. 1.

FIGS. 3a 3b, 3c and 3d show other embodiments of the chopper.

FIGS. 4a and 4b show modifications of part of the circuit arrangement of FIG. 1.

In FIG. 1 the reference numeral 1 denotes a rectifier circuit which converts the mains voltage supplied thereto into a non-stabilized direct voltage. The collector of a switching transistor 2 is connected to one of the two terminals between which this direct voltage is obtained, said transistor being of the npn-type in this embodiment and the base of which receives a pulsatory voltage which originates through a control stage 4 from a modulator 5 and causes transistor 2 to be saturated and cut off alternately. The voltage waveform 3 is produced at the emitter of transistor 2. In order to maintain the output voltage of the circuit arrangement constant, the duration of the pulses provided is varied in modulator 5. A pulse oscillator 6 supplies the pulsatory voltage to modulator 5 and is synchronized by a signal of line frequency which originates from the line oscillator 6' present in the picture display device. This line oscillator 6' is in turn directly synchronized in known manner by pulses 7' of line frequency which are present in the device and originate for example from a received television signal if the picture display device is a television receiver. Pulse oscillator 6 thus generates a pulsatory voltage the repetition frequency of which is the line frequency.

The emitter of switching transistor 2 is connected at one end to the cathode of an efficiency diode 7 whose other end is connected to the second input voltage terminal and at the other end to primary winding 8 of a transformer 9. Pulsatory voltage 3 which is produced at the cathode of efficiency diode 7 is clamped against the potential of said second terminal during the intervals when this diode conducts. During the other intervals the pulsatory voltage 3 assumes the value V i . A charge capacitor 10 and a load 11 are arranged between the other end of winding 8 and the second input voltage terminal. The elements 2,7,8,10 and 11 constitute a so-called chopper producing a direct voltage across charge capacitor 10, provided that capacitor 10 has a sufficiently great value for the line frequency and the current applied to load 11 flowing alternately through switching transistor 2 or through efficiency diode 7. The output voltage V o which is the direct voltage produced across charge capacitor 10 is applied to a comparison circuit 12 which compares the voltage V o with a reference voltage. Comparison circuit 12 generates a direct voltage which is applied to modulator 5 so that the duration of the effective period δ T of switching transistor 2 relative to the period T of pulses 3 varies as a function of the variations of output voltage V 0 . In fact, it is readily evident that output voltage V o is proportional to the ratio δ :

V o = V i . δ

Load 11 of the chopper consists in the consumption of parts of the picture display device which are fed by output voltage V 0 . In a practical embodiment of the circuit arrangement according to FIG. 1 wherein the mains alternating voltage has a nominal effective value of 220 V and the rectified voltage V i is approximately 270 V, output voltage V o for δ = 0.5 is approximately 135 V. This makes it also possible, for example, to feed a line deflection circuit as is shown in FIG. 1 wherein load 11 then represents different parts which are fed by the chopper. Since voltage V o is maintained constant due to pulse duration modulation, the supply voltage of this line deflection circuit remains constant with the favorable result that the line amplitude(= the width of the picture displayed on the screen of the picture display tube) likewise remains constant as well as the EHT required for the final anode of the picture display tube in the same circuit arrangement independent of the variations in the mains voltage and the load on the EHT generator (= variations in brightness).

However, variations in the line amplitude and the EHT may occur as a result of an insufficiently small internal impedance of the EHT generator. Compensation means are known for this purpose. A possibility within the scope of the present invention is to use comparison circuit 12 for this purpose. In fact, if the beam current passes through an element having a substantially quadratic characteristic, for example, a voltage-dependent resistor, then a variation for voltage V o may be obtained through comparison circuit 12 which variation is proportional to the root of the variation in the EHT which is a known condition for the line amplitude to remain constant.

However, variations in the line amplitude and the EHT may occur as a result of an insufficiently small internal impedance of the EHT generator. Compensation means are known for this purpose. A possibility within the scope of the present invention is to use comparison circuit 12 for this purpose. In fact, if the beam current passes through an element having a substantially quadratic characteristic, for example, a voltage-dependent resistor, then a variation for voltage V o may be obtained through comparison circuit 12 which variation is proportional to the root of the variation in the EHT which is a known condition for the line amplitude to remain constant.In addition this facilitates smoothing of voltage V o since the repetition frequency of pulsatory voltage 3 is many times higher than that of the mains and a comparatively small value may be sufficient for charge capacitor 10. If charge capacitor 10 has a sufficiently high value for the line frequency, voltage V o is indeed a direct voltage so that a voltage having the same form as pulsatory voltage 3 is produced across the terminals of primary winding 8. Thus voltages which have the same shape as pulsatory voltage 3 but have a greater or smaller amplitude are produced across secondary windings 13, 14 of transformer 9 (FIG. 1 shows only 2 secondary windings but there may be more). The invention is based on the recognition that one end of each secondary winding is connected to earth while the other end thereof drives a diode, the winding sense of each winding and the direction of conductance of each diode being chosen to be such that these diodes conduct during the same period as does efficiency diode 7. After smoothing, stabilized supply voltages, for example, at terminal 15 are generated in this manner at the amplitudes and polarities required for the circuit arrangements present in the picture display device. In FIG. 1 the voltage generated at terminal 15 is, for example, positive relative to earth. It is to be noted that the load currents of the supply voltages obtained in this manner cause a reduction of the switching power which is economized by efficiency diode 7. The sum of all diode currents including that of diode 7 is in fact equal to the current which would flow through diode 7 if no secondary winding were wound on transformer 9 and if no simultaneous diode were used. This reduction may be considered an additional advantage of the circuit arrangement according to the invention, for a diode suitable for smaller powers may then be used. However, it will be evident that the overall secondary load must not exceed the primary load since otherwise there is the risk of efficiency diode 7 being blocked so that stabilization of the secondary supply voltages would be out of the question.

It is to be noted that a parabola voltage of line frequency as shown at 28 is produced across the charge capacitor 10 if this capacitor is given a smaller capacitance so that consequently the so-called S-correction is established.

In FIG. 1 charge capacitors are arranged between terminals 15 etc. and earth so as to ensure that the voltages on these points are stabilized direct voltages. If in addition the mean value of the voltage on one of these terminals has been made equal to the effective value of the alternating voltage which is required for heating the filament of the picture display tube present in the picture display device, this voltage is suitable for this heating. This is a further advantage of the invention since the cheap generation of a stabilized filament voltage for the picture display tube has always been a difficult problem in transistorized arrangements.

A further advantage of the picture display device according to the invention is that transformer 9 can function as a separation transformer so that the different secondary windings can be separated from the mains and their lower ends can be connected to ground of the picture display device. The latter step makes it possible to connect a different apparatus such as, for example, a magnetic recording and/or playback apparatus to the picture display device without earth connection problems occurring.

In FIG. 1 the reference numeral 14 denotes a secondary winding of transformer 9 which in accordance with the previously mentioned recognition of the invention can drive line output transistor 16 of the line deflection circuit 17. Line deflection circuit 17 which is shown in a simplified form in FIG. 1 includes inter alia line deflection coils 18 and an EHT transformer 19 a secondary winding 20 of which serves for generating the EHT required for the acceleration anode of the picture display tube. Line deflection circuit 17 is fed by the output voltage V o of the chopper which voltage is stabilized due to the pulse duration modulation with all previously mentioned advantages. Line deflection circuit 17 corresponds, for example, to similar arrangements which have been described in U.S. Pat. No. 3,504,224 issued Mar. 31, 1970 to J.J. Reichgelt et al., U.S. patent application Ser. No. 737,009 filed June 14, 1968 by W. H. Hetterscheid and U.S. application Ser. No. 26,497 filed April 8, 1970 by W. Hetterscheid et al. It will be evident that differently formed lined deflection circuits are alternatively possible.

It will now be shown that secondary winding 14 can indeed drive a line deflection circuit so that

switching transistor 2 can function as a driver for the line deflection. FIGS. 2a and b show the variation as a function of time of the current i C which flows in the collector of transistor 16 and of the drive voltage v 14 across the terminals of secondary winding 14. During the flyback period (0, t 1 ) transistor 16 must be fully cut off because a high voltage peak is then produced at its collector; voltage v 14 must then be absolutely negative. During the scan period (t 1 , t 4 ) a sawtooth current i C flows through the collector electrode of transistor 16 which current is first negative and then changes its direction. As the circuit arrangement is not free from loss, the instant t 3 when current i C becomes zero lies, as is known, before the middle of the scan period. At the end t 4 of the scan period transistor 16 must be switched off again. However, since transistor 16 is saturated during the scan period and since this transistor must be suitable for high voltages and great powers so that its collector layer is thick, this transistor has a very great excess of charge carriers in both its base and collector layers. The removal of these charge carriers takes a period t s which is not negligible whereafter the transistor is indeed switched off. Thus the fraction δ T of the line period T at which v 14 is positive must end at the latest at the instant (t 4 - t s ) located after the commencement (t = 0) of the previous flyback.

The time δ T may be initiated at any instant t 2 which is located between the end t 1 of the flyback period and the instant t 3 when collector current i C reverses its direction. It is true that emitter current flows through transistor 16 at the instant t 2 , but collector current i C is not influenced thereby, at least not when the supply voltage (= V o ) for line deflection circuit 17 is high enough. All this has been described in the U.S. Pat. No. 3,504,224. The same applies to line deflection circuits wherein the collector base diode does not function as an efficiency diode as is the case in the described circuit 17, but wherein an efficiency diode is arranged between collector and emitter of the line output transistor. In such a case the negative part of the current i C of FIG. 2a represents the current flowing through the said efficiency diode.

After the instant t 3 voltage v 14 must be positive. In other words, the minimum duration of the period T when voltage v 14 must be positive is (t 4 - t s ) - t 3 whilst the maximum duration thereof is (t 4 - t s ) - t 1 . In a television system employing 625 lines per raster the line period t 4 is approximately 64 μus and the flyback period is approximately 12 μus. Without losses in the circuit arrangement instant t 3 would be located approximately 26 μus after the instant t 1 , and with losses a reasonable value is 22 μus which is 34 μus after the commencement of the period. If for safety's sake it is assumed that t s lasts approximately 10 μus, the extreme values of δ T are approximately 20 and 42 μus and consequently the values for δ are approximately 0.31 and 0.66 at a mean value which is equal to approximately 0.49. It was previously stated that a mean value of δ = 0.5 was suitable. Line deflection circuit 17 can therefore indeed be used in combination with the chopper in the manner described, and the relative variation of δ may be (0.66 - 0.31) : 0.49 = 71.5 percent. This is more than necessary to obviate the variations in the mains voltage or in the various loads and to establish the East-West modulation and ripple compensation to be described hereinafter. In fact, if it is assumed that the mains voltage varies between -15 and +10 percent of the nominal value of 220 V, while the 50 Hz ripple voltage which is superimposed on the input voltage V i has a peak-to-peak value of 40 V and V i is nominally 270 V, then the lowest occurring V i is:

0.85 × 270 V - 20 V = 210 V and the highest occurring V i is

1.1 × 270 V + 20 V = 320 V. For an output voltage V o of 135 V the ratio must thus vary between

δ = 135 : 210 = 0.64 and δ = 135 : 320 = 0.42.

A considerable problem presenting itself is that of the simultaneous or non-simultaneous drive of line output transistor 16 with switching transistor 2, it being understood that in case of simultaneous drive both transistors are simultaneously bottomed, that is during the period δ T. This depends on the winding sense of secondary winding 14 relative to that of primary winding 8. In FIG. 1 it has been assumed that the drive takes place simultaneously so that the voltage present across winding 14 has the shape shown in FIG. 2b. This voltage assumes the value n(V i - V o ) in the period δ T and the value -nVo in the period (1 - δ )T, wherein n is the ratio of the number of turns on windings 14 and 8 and wherein V o is maintained constant at nominal mains voltage V o = δ V inom . However, if as a result of an increase or a decrease of the mains voltage V i increases or decreases proportionally therewith, i.e., V i = V i nom + Δ V, the positive portion of V 14 becomes equal to n(V i nom - V o +Δ V) = n [(1 -δ)V i nom +ΔV] = n(0.5 V inom +ΔV) if δ = 0.5 for V i = V i nom. Relatively, this is a variation which is twice as great. For example, if V i nom = 270 V and V o = 135 V, a variation in the mains voltage of from -15 to +10 percent causes a variation of V i of from -40.5 V to +27 V which ranges from -30 to +20 percent of 135 V which is present across winding 8 during the period δ T. The result is that transistor 16 can always be bottomed over a large range of variation. If the signal of FIG. 2b would be applied through a resistor to the base of transistor 16, the base current thereof would have to undergo the same variation while the transistor would already be saturated in case of too low a voltage. In this case it is assumed that transformer 9 is ideal (without loss) and that coil 21 has a small inductance as is explained in the U.S. patent application Ser. No. 737,009 above mentioned. It is therefore found to be desirable to limit the base current of transistor 16.

This may be effected by providing a coil 22 having a large value inductance, approximately 100 μH, between winding 14 and the small coil 21. The variation of said base current i b is shown in FIG. 2c but not to the same scale as the collector current of FIG. 2a. During the conducting interval δ T current i b varies as a linear function of time having a final value of wherein L represents the inductance of coil 22. This not only provides the advantage that this final value is not immediately reached, but it can be shown that variation of this final value as a function of the mains voltage has been reduced, for there applies at nominal mains voltage that: If the mains voltage V i = V i nom +Δ V, then ##SPC1## because V i nom = 2 V o . Thus this variation is equal to that of the mains voltage and is not twice as great.

During switching off, t 2 , of transistor 16 coil 22 must exert no influence and coil 21 must exert influence which is achieved by arranging a diode 23 parallel to coil 22. Furthermore the control circuit of transistor 16 in this example comprises the two diodes 24 and 25 as described in U.S. application Ser. No. 26,497 above referred to, wherein one of these diodes, diode 25 in FIG. 1, must be shunted by a resistor.

During switching off, t 2 , of transistor 16 coil 22 must exert no influence and coil 21 must exert influence which is achieved by arranging a diode 23 parallel to coil 22. Furthermore the control circuit of transistor 16 in this example comprises the two diodes 24 and 25 as described in U.S. application Ser. No. 26,497 above referred to, wherein one of these diodes, diode 25 in FIG. 1, must be shunted by a resistor.The control circuit of transistor 16 may alternatively be formed as is shown in FIG. 4. In fact, it is known that coil 21 may be replaced by the parallel arrangement of a diode 21' and a resistor 21" by which the inverse current can be limited. To separate the path of the inverse current from that of the forward current the parallel arrangement of a the diode 29' and a resistor 29" must then be present. This leads to the circuit arrangement shown in the upper part of FIG. 4. This circuit arrangement may now be simplified if it is noted that diodes 25 and 21' on the one hand and diodes 23 and 29' on the other hand are series-arranged. The result is shown in the lower part of FIG. 4 which, as compared with the circuit arrangement of FIG. 1, employs one coil less and an additional resistor.

FIG. 3 shows possible modifications of the chopper. FIG. 3a shown in a simplified form the circuit arrangement according to FIG. 1 wherein the pulsatory voltage present across the connections of windings 8 has a peak-to-peak amplitude of V i - V o = 0.5 V i for δ = 0.5, As has been stated, the provision of coil 22 gives a relative variation for the base current of transistor 16 which is equal to that of the mains voltage. In the cases according to FIG. 3b, 3c and 3d the peak-to-peak amplitude of the voltage across winding 8 is equal to V i so that the provision of coil 22 results in a relative variation which is equal to half that of the mains voltage which is still more favorable than in the first case.

Transistors of the npn type are used in FIG. 3. If transistors of the pnp type are used, the relevant efficiency diodes must of course be reversed.

In this connection it is to be noted that it is possible to obtain an output voltage V o with the aid of the modifications according to FIGS. 3b, c and d, which voltage is higher than input voltage V i . These modifications may be used in countries such as, for example, the United of America or France where the nominal mains voltage is 117 or 110 V without having to modify the rest of the circuit arrangement.

The above-mentioned remark regarding the sum of the diode currents only applies, however, for the modifications shown in FIGS. 3a and d.

If line output transistor 16 is not simultaneously driven with switching transistor 2, efficiency diodes 7 conducts simultaneously with transistor 16 i.e., during the period which is denoted by δ T in FIGS. 1 and 2b. During that period the output voltage V o of the chopper is stabilized so that the base current of transistor 16 is stabilized without further difficulty. However, a considerable drawback occurs. In FIG. 1 the reference numeral 26 denotes a safety circuit the purpose of which is to safeguard switching transistor 2 when the current supplied to load 11 and/or line deflection circuit 17 becomes to high, which happens because the chopper stops. After a given period output voltage V o is built up again, but gradually which means that the ratio δ is initially small in the order of 0.1. All this is described in U.S. patent No. 3,629,686. The same phenomenon occurs when the display device is switched on. Since δ = 0.1 corresponds to approximately 6 μs when T = 64 μs, efficiency diode 7 conducts in that case for 64 - 6 = 58 μus so that transistor 16 is already switched on at the end of the scan or at a slightly greater ratio δ during the flyback. This would cause an inadmissibly high dissipation. For this reason the simultaneous drive is therefore to be preferred.

The line deflection circuit itself is also safeguarded: in fact, if something goes wrong in the supply, the driver voltage of the line deflection circuit drops out because the switching voltage across the terminals of primary winding 8 is no longer present so that the deflection stops. This particularly happens when switching transistor 2 starts to constitute a short-circuit between emitter and collector with the result that the supply voltage V o for the line deflection circuit in the case of FIG. 1 becomes higher, namely equal to V i . However, the line output transformer is now cut off and is therefore also safe as well as the picture display tube and other parts of the display device which are fed by terminal 15 or the like. However, this only applies to the circuit arrangement according to FIG. 1 or 3a.

Pulse oscillator 6 applies pulses of line frequency to modulator 5. It may be advantageous to have two line frequency generators as already described, to wit pulse oscillator 6 and line oscillator 6' which is present in the picture display device and which is directly synchronized in known manner by line synchronizing pulses 7'. In fact, in this case line oscillator 6' applies a signal of great amplitude and free from interference to pulse oscillator 6. However, it is alternatively possible to combine pulse oscillator 6 and line oscillator 6' in one single oscillator 6" (see FIG. 1) which results in an economy of components. It will be evident that line oscillator 6' and oscillator 6" may alternatively be synchronized indirectly, for example, by means of a phase discriminator. It is to be noted neither pulse oscillator 6, line oscillator 6' and oscillator 6" nor modulator 5 can be fed by the supply described since output voltage V o is still not present when the mains voltage is switched on. Said circuit arrangements must therefore be fed directly from the input terminals. If as described above these circuit arrangements are to be separated from the mains, a small separation transformer can be used whose primary winding is connected between the mains voltage terminals and whose secondary winding is connected to ground at one end and controls a rectifier at the other end.

Capacitor 27 is arranged parallel to efficiency diode 7 so as to reduce the dissipation in switching transistor 2. In fact, if transistor 2 is switched off by the pulsatory control voltage, its collector current decreases and its collector-emitter voltage increases simultaneously so that the dissipated power is not negligible before the collector current has becomes zero. If efficiency diode 7 is shunted by capacitor 27 the increase of the collector-emitter voltage is delayed i.e., this voltage does not assume high values until the collector current has already been reduced. It is true that in that case the dissipation in transistor 2 slightly increases when it is switched on by the pulsatory control voltage but on the other hand since the current flowing through diode 7 has decreased due to the presence of the secondary windings, its inverse current is also reduced when transistor 2 is switched on and hence its dissipation has become smaller. In addition it is advantageous to delay these switching-on and switching-off periods to a slight extent because the switching pulses then contain fewer Fourier components of high frequency which may cause interferences in the picture display device and which may give rise to visible interferences on the screen of the display tube. These interferences occupy a fixed position on the displayed image because the switching frequency is the line frequency which is less disturbing to the viewer. In a practical circuit wherein the line frequency is 15,625 Hz and wherein switching transistor 2 is an experimental type suitable for a maximum of 350 V collector-emitter voltage or 1 A collector current and wherein efficiency diode 7 is of the Philips type BA 148 the capacitance of capacitor 27 is approximately 680 pF whilst the load is 70 W on the primary and 20 W on the secondary side of transformer 9. The collector dissipation upon switching off is 0.3 W (2.5 times smaller than without capacitor 27) and 0.7 W upon switching on.

As is known the so-called pincushion distortion is produced in the picture display tubes having a substantially flat screen and large deflection angles which are currently used. This distortion is especially a problem in color television wherein a raster correction cannot be brought about by magnetic means. The correction of the so-called East-West pincushion distortion i.e., in the horizontal direction on the screen of the picture display tube can be established in an elegant manner with the aid of the circuit arrangement according to the invention. In fact, if the voltage generated by comparison circuit 12 and being applied to modulator 5 for duration-modulating pulsatory voltage 3 is modulated by a parabola voltage 28 of field frequency, pulsatory voltage 3 is also modulated thereby. If the power consumption of the line deflection circuit forms part of the load on the output voltage of the chopper, the signal applied to the line deflection coils is likewise modulated in the same manner. Conditions therefore are that the parabola voltage 28 of field frequency has a polarity such that the envelope of the sawtooth current of line frequency flowing through the line deflection coils has a maximum in the middle of the scan of the field period and that charge capacitor 10 has not too small an impedance for the field frequency. On the other hand the other supply voltages which are generated by the circuit arrangement according to the invention and which might be hampered by this component of field frequency must be smoothed satisfactorily.

A practical embodiment of the described example with the reference numerals given provides an output for the supply of approximately 85 percent at a total load of 90 W, the internal resistance for direct current loads being 1.5 ohms and for pulsatory currents being approximately 10 ohms. In case of a variation of ± 10 percent of the mains voltage, output voltage V o is stable within 0.4 V. Under the nominal circumstances the collector dissipation of switching transistor 2 is approximately 2.5 W.

Since the internal resistance of the supply is so small, it can be used advantageously, for example, at terminal 15 for supplying a class-B audio amplifier which forms part of the display device. Such an amplifier has the known advantages that its dissipation is directly proportional to the amplitude of the sound to be reproduced and that its output is higher than that of a class-A amplifier. On the other hand a class-A amplifier consumes a substantially constant power so that the internal resistance of the supply voltage source is of little importance. However, if this source is highly resistive, the supply voltage is modulated in the case of a class-B amplifier by the audio information when the sound intensity is great which may detrimentally influence other parts of the display device. This drawback is prevented by means of the supply according to the invention.

The 50 Hz ripple voltage which is superimposed on the rectified input voltage V i is compensated by comparison circuit 12 and modulator 5 since this ripple voltage may be considered to be a variation of input voltage V i . A further compensation is obtained by applying a portion of this ripple voltage with suitable polarity to comparison circuit 12. It is then sufficient to have a lower value for the smoothing capacitor which forms part of rectifier circuit 1 (see FIG. 3). The parabola voltage 28 of field frequency originating from the field time base is applied to the same circuit 12 so as to correct the East-West pincushion distortion.

PHILIPS 26CP2402/08R CHASSIS K12Z PHILIPS TRD 2 (Tuning Remote Digital) Search type tuning system Chassis K12z:Dics-Digital Tuning System For TV Receivers" by N.V. Philips' Gloeilampenfabrieken, Netherlands, 2/1977

A wide variety of "search" or "signal seeking" tuning systems for radio and television receivers are known which provide for automatically tuning only those channels which have acceptable reception characteristics and for skipping past thosechannels which have unacceptable reception characteristics. Such tuning systems typically include a number of signal detectors for determining when a received RF carrier has acceptable reception characteristics. For example, a search type tuning systemfor a television receiver may include: an AFT (automatic fine tuning) detector for determining when an IF carrier derived from the received RF carrier has a frequency within a predetermined range of its desired value; and AGC (automatic gain control)detector for determining when the received RF carrier has an amplitude greater than a predetermined value; and a synchronization detector to determine when synchronization pulses derived from the received RF carrier have the proper frequency.

Tuning systems are also known which include a memory having memory locations associated with each channel in a tuning range for storing information as to whether the associated station or channel is preferred or not. Such "memory" type tuningsystems may be utilized as an alternative to the "search" type tuning systems to select only those channels with acceptable reception characteristics in a given location.

Both "search" and "memory" type tuning systems require a considerable amount of complex and expensive circuitry, in addition to the basic tuning system for tuning each channel in a tuning range, for tuning only those channels with acceptablereception characteristics. Thus, there is a need for a tuning system which requires only a relatively small amount of circuitry in addition to the basic tuning system for tuning only channels with acceptable reception characteristics.

A)- A television tuning system employs a frequency synthesizer system for establishing the tuning of the receiver. A first programmable frequency divider controlled by a reversible counter is connected between the output of a reference oscillator and a phase comparator to which the output of the local oscillator, after passing through another programmable frequency divider, also is applied. The phase comparator output is a tuning voltage used to control the tuning of the local oscillator. A logic circuit is coupled to sense predetermined relationships of signals from a picture carrier detector, a sound carrier detector, an AFT discriminator circuit, and the presence of vertical synchronization signal components for changing the count in the reversible binary counter to adjust the first programmable frequency divider to compensate for channel frequency offsets which may occur in excess of the pull-in range of the AFT discriminator circuit. To permit operation of the

receiver as a signal seek receiver, a pair of signal seek pushbuttons for the "up" and for the "down" direction, respectively, are provided. Operation of either of these pushbuttons functions in conjunction with further logic circuitry and in conjunction with timing circuitry to automatically step tune the receiver channel-by-channel in the selected direction until a channel with a signal present is sensed by the first logic circuit, whereupon the signal seek circuit operation is disabled until one or the other of the signal seek pushbuttons is reactivated.

1. A frequency synthesizer signal seek tuning system for a tuner of a television receiver capable of receiving a composite television signal, said system including in combination:

reference oscillator means providing a reference signal at a predetermined frequency;

local oscillator means in the tuner providing a variable output frequency in response to the application of a control signal thereto;

a programmable frequency divider having an input coupled to said reference oscillator means for producing an output signal having a frequency which is a programmable fraction of the frequency of the signal applied to the input thereto from saidreference oscillator means;

means coupled to the output of said programmable frequency divider and the output of said local oscillator means for developing a control signal and applying such control signal to said local oscillator means for controlling the frequency ofoperation thereof;

channel selection means coupled to said programmable frequency divider for establishing a predetermined initial programmable fraction therein each time a new channel is selected by said channel selection means;

control means coupled to the output of the tuner of the television receiver and further coupled to said programmable frequency divider for controlling said frequency divider to change the programmable fraction thereof in response to predeterminedconditions of the signals from the tuner; and

signal seek tuning means coupled to said channel selection means and said control means for causing said channel selection means to select a new channel in response to said predetermined conditions of the tuner signals persisting for a predetermined time period.

2. The combination according to claim 1, wherein the composite television signal has at least carrier signal components and synchronizing signal components and further including carrier sensing means coupled to receive at least the carriersignal components of the composite signal from the tuner and providing an output voltage indicative of the tuning of said receiver to a carrier component of said composite signal; and synchronizing signal component sensing means coupled to receive atleast said synchronizing signal components of the composite signal for providing a first predetermined output with synchronizing signal components sensed thereby; wherein said control means is coupled to the outputs of said carrier sensing means andsaid synchronizing signal components sensing means and further coupled to said programmable frequency divider means for changing the programmable fraction thereof in response to first predetermined conditions of signals at the outputs of said carriersensing means and said synchronizing signal components sensing means and the operation of said signal seek tuning means being terminated in response to second predetermined conditions of signals at the outputs of said carrier sensing means and saidsynchronizing signal components sensing means.

3. The combination according to claim 1, further including first and second switches in said signal seek tuning means for initiating a signal seek operation in the "up" and "down" directions, respectively, operation of one of said first andsecond switches causing said channel selection means to select the next channel in the selected direction and establishing said predetermined initial programmable fraction in said programmable frequency divider in response thereto.

4. The combination according to claim 3, wherein said control means terminates operation of said signal seek means in response to detection of second predetermined conditions of the signals from the tuner.

5. The combination according to claim 1, wherein said predetermined conditions of the tuner signals comprise first and second predetermined conditions, respectively; said programmable frequency divider has its input coupled to the output ofsaid reference oscillator means; and wherein said control means includes reversible digital counter means coupled to said programmable frequency divider, and logic circuit means coupled to the output of the tuner for causing said counter means to countin one direction when said first predetermined conditions exist and to count in the opposite direction when said second predetermined conditions exist.

6. The combination according to claim 5, further including additional means coupled to said counter means and coupled to said logic circuit means for inhibiting operation of said signal seek tuning means and for preventing a change in the countof said counter means when third predetermined signal conditions exist in the tuner output.

7. The combination according to claim 6, further including a second programmable frequency divider coupled to the output of said local oscillator means and producing an output signal having a frequency which is a programmable fraction of thefrequency of the signal applied to the input thereto from said local oscillator means; and wherein said channel selection means is further coupled to said second programmable frequency divider for controlling said second programmable frequency dividerto establish the programmable fraction thereof each time a new channel is selected by said channel selection means.

B)- A tuning system for a television receiver includes a local oscillator which is controlled first by a phase lock loop arrangement and then by an AFT discriminator arrangement for tuning the receiver to non-standard as well as standard frequency carriers. The phase lock loop arrangement includes a programmable divider for dividing the local oscillator frequency by a programmable factor corresponding to the presently selected channel. When the local oscillator is being controlled by the AFT discriminator arrangement, the count accumulated by the programmable divider during a reference interval determines how far the local oscillator frequency has drifted from its nominal value. If a predetermined frequency offset has been exceeded, control is returned to phase lock loop control and the programmable factor is incrementally changed.

1. In a system for tuning a television receiver to the various channels a viewer may select, apparatus comprising:

local oscillator means for generating a local oscillator signal;

counter means for generating a frequency divided signal by counting a predetermined number of periods of said local oscillator signal, said predetermined number being proportional to the frequency of said local oscillator signal;

means for generating a reference frequency signal;

phase control means for generating a control signal representing the phase and frequency deviation between said frequency divided signal and said reference frequency signal;

mode switching means for selectively coupling said control signal to said local oscillator means; said mode switching means initially coupling said control signal to said local oscillator means;

said local oscillator means changing the frequency of said local oscillator signal in response to said control signal until said frequency divided signal and said reference frequency signal to be in a predetermined phase and frequency relation;

said counter means accumulating a nominal number of counts during a predetermined portion of said frequency divided signal when said frequency divided signal and said reference signal are in said predetermined phase and frequency relationship;

means for generating a lock signal when said frequency divided signal and said reference frequency signal are in said predetermined phase and frequency relationship;

said mode switching means decoupling said control signal from said local oscillator means in response to said lock signal;

means for generating a count signal when said control signal is decoupled from said local oscillator means, said count signal having a duration with a predetermined time relationship to said reference frequency signal;

means responsive to said count signal for disabling said counter means from counting when said control signal is decoupled from said local oscillator means except during the duration of said count signal; and

means for generating an offset signal representing the deviation between the count accumulated by said counter means during a time interval corresponding to said predetermined portion of said frequency divided signal when said control signal isdecoupled from said local oscillator means and said nominal number of counts, said offset signal being coupled to said mode switching means to control the coupling of said control signal to said local oscillator means.

2. The apparatus recited in claim 1 wherein said means for generating said offset signal includes:

memory means for generating an output signal having a first amplitude when said memory means is set and a second amplitude when said memory means is reset, said output signal being coupled to said mode switching means as said offset signal;

means for resetting said memory means prior to the occurrence of said time interval corresponding to said predetermined portion of said frequency divided signal when said control signal is decoupled from said local oscillator means;

means for setting said memory means if the count accumulated by said counter during said time interval corresponding to said predetermined portion of said frequency divided signal when said control signal is decoupled from said local oscillatormeans is less than said nominal number of counts by a first predetermined deviation; and

means for resetting said memory means if the count accumulated by said counter means during said time interval corresponding to said predetermined portion of said frequency divided signal when said control signal is decoupled from said localoscillator means is greater than said nominal number of counts by a second predetermined deviation.

3. The apparatus recited in claim 1 wherein said counter means derives said frequency divided signal by counting a first number of periods during a first portion of said frequency divided signal and by counting a second number of periods duringa second portion of said frequency divided signal.

4. The apparatus recited in claim 3 wherein the various channels a viewer may select are partitioned into frequency bands, said first number is related to the channel selected by a viewer and said second number is related to the frequency bandin which the selected channel resides.

5. The apparatus recited in claim 4 wherein said predetermined portion is at least a part of said second portion.

6. The apparatus recited in claim 5 wherein said counter includes:

variable modulus frequency divider means for selectively dividing the frequency of said local oscillator signal by a first factor or a second factor, said first factor being related to the frequency spacing between channels in at least one ofsaid bands;

decade counter means for counting periods of the output signal of said variable modulus frequency divider;

channel number comparator means for generating a channel match signal when the number of periods counted by said decade counter means equals said first number, said decade counter means being reset in response to said channel match signal;

first factor stop comparator means for generating a first factor stop signal when the number of periods counted by said decade counter means equals a third number, said third number being also related to the band in which the selected channelresides but less than said second number, said variable modulus divider means being caused to divide by said second factor in response to said first factor stop signal; and

added count comparator means for generating an added count match signal when the number of periods counted by said decade counter means equals said second number, said decade counter means being reset in response to said added count match signal,said variable modulus divider means being caused to divide by said first factor in response to said added count match signal.

7. The apparatus recited in claim 6 wherein said nominal number of counts equals said second number.

8. The apparatus recited in claim 7 wherein said means for generating said offset signal includes means for resetting at least said decade counter means and for causing said variable modulus divider to divide by said first factor in response tothe initiation of said count signal.

9. The apparatus recited in claim 7 wherein said means for generating said offset signal includes:

memory means for generating an output signal when said memory means is set and a second amplitude when said memory means is reset, said output signal being coupled to said mode switching means as said offset signal;

means for resetting said memory means prior to the occurrence of said first factor stop signal during the duration of said count signal when said control signal is decoupled from said local oscillator;

means for inhibiting the generation of said added count signal when said control signal is decoupled from said local oscillator;

means for setting said memory means if the count accumulated by said counter means after said first factor stop signal when said control signal is decoupled from said local oscillator means is less than said second number by a first predetermineddeviation; and

means for resetting said memory means if the count accumulated by said counter means after said first factor stop signal when said control signal is decoupled from said local oscillator means is greater than said second number by a secondpredetermined deviation.

10. The apparatus recited in claim 9 wherein said means for generating said offset signal includes means for repetitively generating said offset signal.

11. The apparatus recited in claim 1 wherein said means for disabling said counter means includes input switching means for selectively decoupling said local oscillator signal from said counter means when said control signal is decoupled fromsaid local oscillator means except in response to said count signal; and

said counter means includes means for generating an illegal signal when an illegal channel has been selected;

said input switching means also decoupling said local oscillator signal from said counter means in response to said illegal signal.

12. The apparatus recited in claim 11 wherein:

said means for generating said illegal signal includes band selection means for generating a band traversed signal whenever the count accumulated by said counter corresponds to the boundary of a band and means for generating a band signalrepresenting the band in which the selected channel resides in accordance with which of said band traversed signals have been generated during said first portion of said frequency divided signal, said means for generating a band signal generating saidillegal signal when a band signal is not generated.

13. The apparatus recited in claim 11 wherein said means for generating said reference frequency also includes means for deriving a signal having a predetermined frequency; and said input means includes means for coupling said signal having apredetermined frequency to said counter means in response to said illegal signal.

Description: The present invention pertains to television tuning systems including a phase locked loop frequency synthesizerand particularly pertains to frequency counters which may be utilized in such systems.

In concurrently filed U.S. patent application Ser. No. 70,849, and now U.S. Pat. No. 4,031,549 by Henderson et al., assigned to the same assignee as the present invention, there is described a tuning device system for a television receiverwhich includes a phase locked loop for tuning a local oscilator to the nominal local oscillator frequencies required to tune the receiver to RF carriers at standard broadcast frequencies allocated to the various channels a viewer may select. The tuningsystem also includes an automatic fine tuning (AFT) frequency discriminator for tuning the local oscillator to minimize any deviation between the frequency of an actual picture carrier and the nominal picture carrier frequency. If the receiver iscoupled to a television distribution system which provides RF carriers having nonstandard frequencies arbitrarily near respective ones of the standard broadcast frequencies, when the phase locked loop has achieved lock at a nominal frequency, a modecontrol unit selectively couples the discriminator and a frequency drift control circuit to the local oscillator. If the frequency of the local oscillator drifts more than a predetermined offset from the frequency synthesized under phase locked loopcontrol because no carrier has been detected by the discriminator, discriminator and drift control are terminated so that the receiver will not be tuned to an undesired carrier such as, for example, the lower adjacent channel sound carrier, and phaselocked loop control is reinitiated to synthesize a local oscillator signal having a frequency incremented from the frequency of the originally synthesized local oscillator signal by a predetermined amount. After the phase locked loop is locked at anincremented frequency, discriminator control is again initiated. If, during this cycle of discriminator control, the local oscillator again drifts more than the predetermined offset from the incremented local oscillator frequency because no carrier isdetected by the discriminator, phase locked loop control is again reinitiated to synthesize a local oscillator signal having a frequency decremented from the frequency of the originally synthesized local oscillator signal by a predetermined amount. Ifduring any discriminator control cycle the local oscillator has not drifted further than the predetermined offset because the discriminator has tuned the local oscillator to a carrier within the predetermined offset, phase locked loop control is notreinitiated and the tuning sequence is complete.

In order to reduce the complexity, and therefore the cost, of an implementation of such a tuning system, it is desirable that individual potions of the system be capable of performing more than one function. For example, in copending UnitedStates Patent Application Ser. No. 663,097 filed for R. M. Rast on Feb. 27, 1976, and now U.S. Pat. No. 4,009,439 and assigned to the same assignee as the present invention, which is hereby incorporated by reference, there is described a frequencydivider for a television tuning phase locked loop tuning system. For each channel a viewer selects, the divider divides the frequency of the local oscillator signal by a number proportional to the nominal local oscillator frequency by forming a signalincluding first and second portions having durations respectively equal to first and second numbers of periods of the local oscillator signal. The first number is related to the selected channel number. The second number is related to the frequencyband in which the selected channel resides. To generate signals including in which band the selected channel resides for use in the phase locked loop itself and in the local oscillator to control its frequency range, a band selection unit is included asan integral part of the divider.

In accordance with the present invention, a programmable counter which may be used, for example, in a phase locked loop portion of a tuning system of the type decribed in the concurrently filed Henderson et al. application referenced above todivide the frequency of the local oscillator by a number proportional to the nominal local oscillator frequency for a selected channel is arranged so that it may also serve to generate a signal indicating whether or not the frequency of the localoscillator has drifted beyond a predetermined frequency offset after phase locked loop control of the local oscillator has been terminated. When the local oscillator is under phase locked loop control, the programmable counter accumulates a nominalnumber of counts during a predetermined portion of its output signal. Means are provided for generating a count signal after phase locked loop control of the local oscillator has been terminated. The count signal has a duration with a predeterminedtime relationship to a reference signal to which the local oscillator signal is locked when the local oscillator is under phase locked loop control. The counter is disabled from counting when the local oscillator is not under phase locked loop controlexcept during the duration of the count signal. Offset detection means, in response to the count signal, generates an offset signal representing the deviation between the count accumulated during a time interval corresponding to the predeterminedportion after phase locked loop control of the local oscillator has been terminated to determine how far the frequency of the local oscillator has drifted from the frequency synthesized under phase locked loop control.

C)- A tuning system for a television receiver includes a phase locked loop (PLL) configuration and an automatic fine tuning (AFT) configuration which are selectively enabled to operate to tune the receiver to nonstandard as well as standard frequency RF carriers which may be provided by cable and master antenna systems. After the selection of a new channel, the operations of the PLL and AFT configurations are sequentially enabled by a mode control apparatus. During the operation of the AFT configuration, an offset detector determines when the frequency of the local oscillator signal is caused to be more than a predetermined offset from its value established during the previous operation of the PLL configuration. In response, the mode control unit reestablishes the operation of the PLL configuration. Channel selection apparatus causes a new channel to be selected after a predetermined number of alternate operating cycles of the two configurations.

1. Apparatus for selectively tuning a receiver to any one of a plurality of RF carriers associated with respective channels, comprising:

local oscillator means for generating a local oscillator signal;

mixer means for combining a selected one of said RF carriers with said local oscillator signal to derive an IF signal having at least one carrier with a nominal frequency value;

phase locked loop (PLL) means for selectively controlling said local oscillator means when enabled to operate to cause said local oscillator signal to have a programmed frequency substantially equal to the product of a programmable factor and the frequency of a frequency reference signal;

programmable fac

tor control means for determining programmable factor in accordance with the channel selected and for generating a CHANGE signal when a new channel is selected;

lock means for generating a LOCK signal when said local oscillator signal has a frequency substantially equal to said programmed frequency;

automatic fine tuning (AFT) means for selectively controlling said local oscillator means when enabled to operate to reduce a deviation between the actual frequency of said IF carrier and said nominal frequency value;

offset detector means for generating an OFFSET signal when the frequency of said local oscillator signal is caused to be offset from said programmed frequency by a predetermined amount during the operation of said AFT means;

mode control means for enabling the operation of said PLL means in response to said CHANGE signal, for enabling the operation of said AFT means in response to said LOCK signal and for again enabling the operation of said PLL means in response to said OFFSET signal; and

channel selection means for causing said programmable factor control means to select the programmable factor associated with the next channel when said OFFSET signal is generated a predetermined number of times.

2. The appara

tus recited in claim 1 wherein:

tus recited in claim 1 wherein: said predetermined number of times is equal to one.

3. The apparatus recited in claim 1 wherein:

said programmable factor control means is coupled to counter means for counting the number of times said OFFSET signal is generated to change said programmable factor by an increment less than the difference between programmable factors associated with respective adjacent channels when said OFFSET signal is generated a second predetermined number of times less than said first mentioned predetermined number of times; and

said channel selection means is also coupled to said counter means for causing said programmable factor control means to select the programmable factor associated with the next channel when said OFFSET signal is generated said first mentioned predetermined number of times.

4. The apparatus recited in claim 3 wherein:

said programmable factor control means increases said programmable factor by said increment in response to a first generation of said OFFSET signal and decreases said programmable factor by said increment in response to a second generation of said OFFSET signal and changes said programmable factor to the value associated with the next channel in response to a third generation of said OFFSET signal.

5. The apparatus recited in claim 4 wherein:

said programmable factor control means includes inhibiting means for inhibiting said programmable factor control means from changing said programmable factor to the value in response to said OFFSET signal after a predetermined time longer than the time required to tune said receiver to a selected channel.

The present invention relates to search type tuning systems.

A wide variety of "search" or "signal seeking" tuning systems for radio and television receivers are known which provide for automatically tuning only those channels which have acceptable reception characteristics and for skipping past those channels which have unacceptable reception characteristics. Such tuning systems typically include a number of signal detectors for determining when a received RF carrier has acceptable reception characteristics. For example, a search type tuning system for a television receiver may include: an AFT (automatic fine tuning) detector for determining when an IF carrier derived from the received RF carrier has a frequency within a predetermined range of its desired value; and AGC (automatic gain control) detector for determining when the received RF carrier has an amplitude greater than a predetermined value; and a synchronization detector to determine when synchronization pulses derived from the received RF carrier have the proper frequency.

Tuning systems are also known which include a memory having memory locations associated with each channel in a tuning range for storing information as to whether the associated station or channel is preferred or not. Such "memory" type tuning systems may be utilized as an alternative to the "search" type tuning systems to select only those channels with acceptable reception characteristics in a given location.

Both "search" and "memory" type tuning systems require a considerable amount of complex and expensive circuitry, in addition to the basic tuning system for tuning each channel in a tuning range, for tuning only those channels with acceptable reception characteristics. Thus, there is a need for a tuning system which requires only a relatively small amount of circuitry in addition to the basic tuning system for tuning only channels with acceptable reception characteristics.

SUMMARY OF THE PRESENT INVENTION

The present invention is an improvement to the type of electronic tuning system which includes first tuning means for tuning a tuner to standard frequencies associated with respective channels, second tuning means for tuning the tuner to reduce deviations between the frequency of an IF carrier generated by the tuner and its desired or nominal value that may arise due to, e.g., offsets in the frequencies of received RF carriers, and mode switching means for selectively applying the first and second tuning control signals to the tuner. In this type of electronic tuning system, the operation of the first tuning means is enabled after a new channel is selected and the operation of the second tuning means is enabled after the first tuning means has completed its operation. During the operation of the second tuning means, an offset detector determines when the frequency of a local oscillator signal generated by the tuner becomes offset from value established during the operation of the first tuning means and causes the operation of the first tuning means to again be enabled.

In accordance with the present invention, search means are provided in the above described type of electronic tuning system for causing a new channel to be selected if no RF carrier is tuned by the end of a predetermined number of operating cycles of the second tuning means.

PHILIPS 26CP2402/08R CHASSIS K12Z Programmable timer television receiver controllers:

Programmable television receiver controllers which may be manually programmed by a user to select or to limit the viewing selections for random times, typically in one-half hour intervals, throughout a predetermined time period such as a one week time period. Program selections may be made by setting suitable controls for the day, AM or PM, the half hour of the day and the channel desired, and entered into a memory by a push-button control. Thereafter a digital control clock automatically selects the pre-entered information at the appropriate times and provides a control signal which may be used to automatically select the identified channels to the exclusion of all others. Alternatively, the signal may be used to exclude the selected channel from selection manually. In one embodiment, the programmable controller is incorporated in the original design of the television receiver and in a second embodiment, an external controller is disclosed which can be attached to the antenna terminals of a conventional television. Additional embodiments include means for controlling other functions such as the ON-OFF function of the receiver.

1. A programmable television controller comprising:

a random-access memory means for storing data;

storing means for storing data corresponding to channel selections in said memory means at write-addresses corresponding to future time periods, with said storing means including a write-address for application to said memory means means for generating said write-addresses;

read means for reading out said data from said memory means by application of real time related read-addresses thereto when real time coincides with said future time periods and

control means for controlling the reception of a television receiver according to said data read from said memory means.

2. The controller of claim 1 wherein said memory means is a semiconductor memory. 3. The controller of claim 1 wherein said storing means includes a means for generating said write-addresses which is responsive to the position of at least one first switch and a means for generating said data corresponding to channel selections which is responsive to the position of at least one second switch. 4. The controller of claim 1 wherein said controller means controls the reception of said television receiver by limiting the reception to a channel corresponding to said data read from said memory means if said data is present. 5. A programmable television controller comprising: random-access memory means for storing data;

data means for selectively generating data corresponding to a television channel;

write-address means selectively generating a write-address corresponding to a future time for application to said memory means;

program means for selectively storing said data in said memory means at said write-address;

read-address means for generating said read-addresses responsive to real time;

memory read means for applying said read-addresses to said memory means for reading out said data stored in said memory means; and

control means for controlling the reception of a television receiver according to said data read from said memory means.

6. The controller of claim 5 wherein said memory means is a semiconductor memory. 7. The controller of claim 5 wherein said data means comprises at least one switch. 8. The controller of claim 5 wherein said write-address means comprises at least one switch. 9. The controller of claim 5 wherein said program means comprises:

means for normally coupling said read-address means to said memory;

means for normally placing said memory in a read mode;

switching means for momentarily decoupling the read-address means from said memory means, coupling said write-address means to said memory means, and switching said memory means from said read mode to a write mode.

10. The controller of claim 5 wherein said read-addresses are binary coded signals which increment on one-half hour intervals. 11. The controller of claim 5 wherein said control means controls said reception of said television receiver by limiting the reception to a channel corresponding to said data read from said memory means if said data is present. 12. The controller of claim 5 wherein said control means controls the reception of said television receiver by limiting the reception to a channel other than the channel corresponding to said data received from said memory means if said data is present. 13. The controller of claim 5 wherein said control means includes a pretuner means having at least one input for coupling to a television receiver antenna and a pretuner output for coupling to an input on a television receiver, said pretuner means being a means for selectively converting any one of a plurality of multi-frequency television signals present at said pretuner input to a fixed frequency signal. 14. The controller of claim 13 wherein said control means further includes a disable means for disabling said control means thereby preventing reception of any channel when a power source powering said controller is interrupted, said disable means continuing to disable said controller until said disable means is reset. 15. The controller of claim 13 wherein said controller is installed within a controller housing, said controller housing being located outside a television receiver housing which encloses the television receiver controlled by said controller. 16. The controller of claim 13 wherein said pretuner output is for coupling to an antenna input on the television receiver and the frequency of said fixed frequency signal corresponds to a predetermined television signal. 17. The controller of claim 13 wherein said pretuner output is for coupling to an input of an intermediate frequency amplifier stage in the television receiver and the frequency of said fixed frequency signal corresponds to the intermediate frequency amplifier stage frequency of operation. 18. A programmable television controller comprising:

a random-access memory means for storing data;

storing means for storing data corresponding to channel selections in said memory means at write-addresses corresponding to future time periods, with said storing means including a write-address means for generating said write-addresses for application to said memory means;

read means for reading out said data from said memory means by application of real time related read-addresses thereto when real time coincides with said future time periods and,